随着便携式

电子产品、“智能设备”和汽车电子产品的不断普及,对 IC 中嵌入模拟功能的需求也不断增加。这推动了对特定模拟技术的需求,这些技术在整个半导体市场中所占的份额越来越大。

随着便携式电子产品、“智能设备”和汽车电子产品的不断普及,对 IC 中嵌入模拟功能的需求也不断增加。这推动了对特定模拟技术的需求,这些技术在整个半导体市场中所占的份额越来越大。

经过一些简化,模拟技术可以分为三个主要类别:

高功率BiCMOS:主要目标是功率器件的RDSON和击穿电压。通常具有非常广泛的元件类型(双极、CMOS、LDMOS 和 DEMOS 器件),涵盖从低压(LV,几伏)到极高电压(HV,数百伏)的应用。

高速BiCMOS:主要目标是双极器件的速度,以支持高达数百GHz的高速应用。

模拟 CMOS:主要特点是高密度 CMOS 逻辑,以及低寄生、低噪声和高质量无源器件。它们往往是 CMOS 技术的“衍生物”。

静电放电 (ESD) 是静电电荷从人体转移到物体,会在短时间内(数百纳秒)产生高电流(几安培)。ESD 事件可能是由 IC 在制造过程中的人为处理/测试引起的,并可能导致灾难性的损坏。为了保证处理/测试时的 ESD 鲁棒性,每个 IC 都经过标准 ESD 测试,通常是人体模型 (HBM) 和充电器件模型 (CDM)。

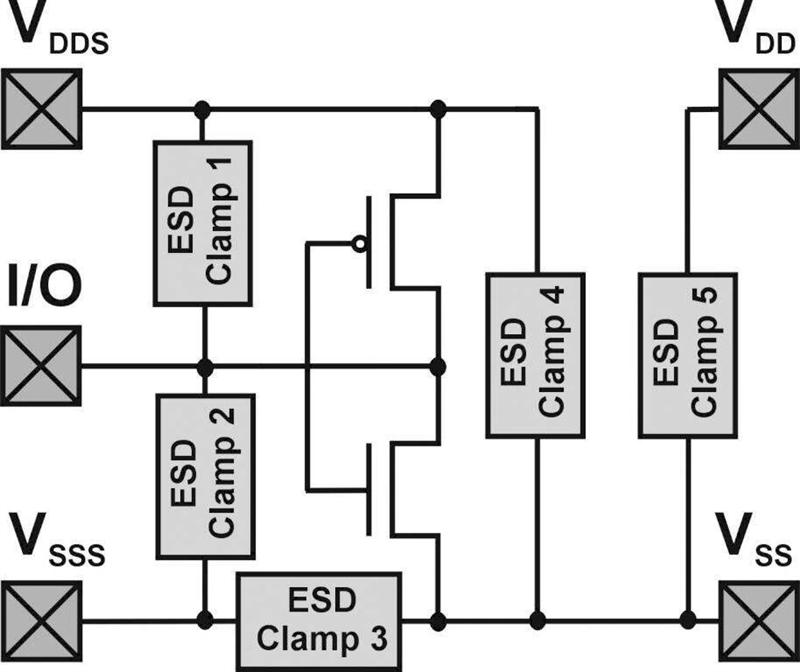

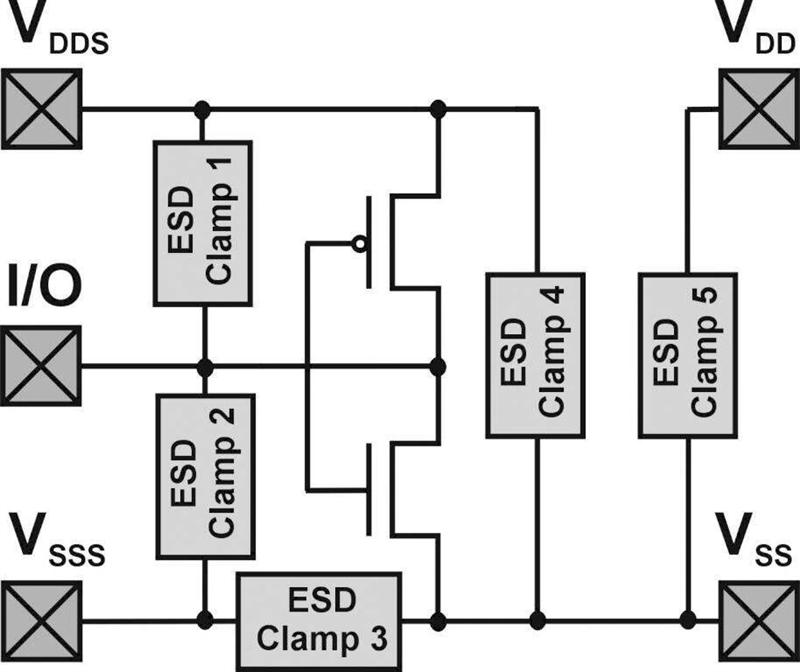

为了达到所需的 ESD 鲁棒性水平,在每个焊盘上添加了专用片上电路(通常称为“ESD 保护”或“ESD 钳位”),以将 ESD 能量吸收到受保护电路的安全水平。在典型的 ESD 保护实施中,每个焊盘到焊盘组合必须具有通过 ESD 保护的有效 ESD 放电路径(图 1)。模拟技术在 ESD 鲁棒性设计方面提出了许多挑战。

ESD 技术挑战

CMOS 和模拟技术之间的一个根本区别在于后者通常是模块化构建的。这允许 IC 设计人员仅选择可用工艺掩模的一部分,以定制设计需求(并非给定工艺中可用的所有组件都可以用于设计)。

从 ESD 设计的角度来看,这意味着 ESD 设计人员必须使用不同的掩

模组支持相同的 ESD 应用。这可能非常具有挑战性,因为 ESD 保护的实际行为很大程度上取决于掩模组。换句话说,可能需要构建同一 ESD 保护的多个版本,具体取决于可用的掩模组。

模拟技术的另一个具有挑战性的方面在于利用模型。的 CMOS 技术的使用寿命只有几年,而模拟技术的使用寿命可能为 10-15 年,甚至 20 年。在此生命周期内产生的应用组合对于 ESD 设计来说是一个相当大的挑战。

漏极扩展 MOS 的ESD 设计挑战

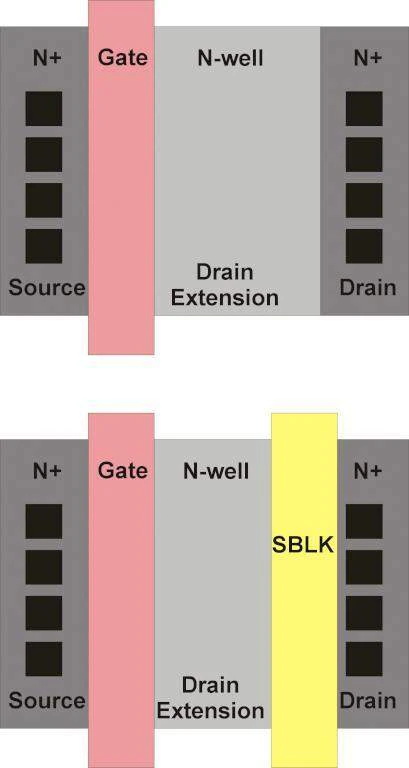

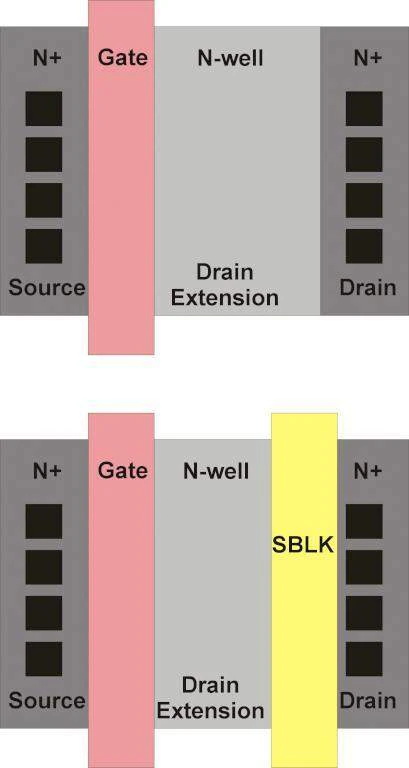

漏极扩展 MOS (DEMOS) 是一种在高掺杂漏极区域或漏极扩展中添加同类型低掺杂区域的器件(图 2)。这会影响额定电压(即击穿增加)和漏极-栅极压降(与栅极氧化物可靠性相关)。另一方面,这种类型的设计会降低驱动电流特性,因为通道通常没有针对该结进行优化。更复杂的版本是横向扩散 MOS (LDMOS),具有更好的电流驱动特性。

从 ESD 角度来看,DEMOS

晶体管具有非常低的 ESD 鲁棒性,即在 ESD 条件下承受高电流密度的能力。DEMOS 的 ESD 弱点是高效 ESD 设计的主要挑战,因为它需要特殊的 ESD 保护电路,该电路在 ESD 事件期间不会使用 DEMOS 晶体管(这会影响面积)。过去 15 年中的多项研究已经解决了这个具体问题,这也得益于在的 CMOS 技术中使用这些组件。

近的一项工作 [1] 表明,阻断高掺杂/低掺杂漏极区域(图 3 中的“SBLK”区域)上的硅化过程可以显着提高 DEMOS 晶体管的 ESD 鲁棒性。

这种结构基本上增加了漏极侧的电阻。虽然其具体影响相当复杂,但它可以被视为一种通过器件整个宽度上的 ESD 电流分布防止电流传导不均匀的方法。

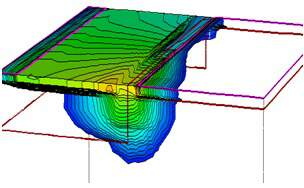

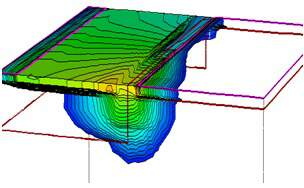

3 维 TCAD 电热仿真清楚地描绘了沿器件整个宽度的均匀 ESD 电流分布,以及漏极区域硅化物的阻挡(图 4)。这将允许具有这种结构的 DEMOS 耗散一些 ESD 能量,从而减少对 ESD 保护设计的限制。

高压有源 FET

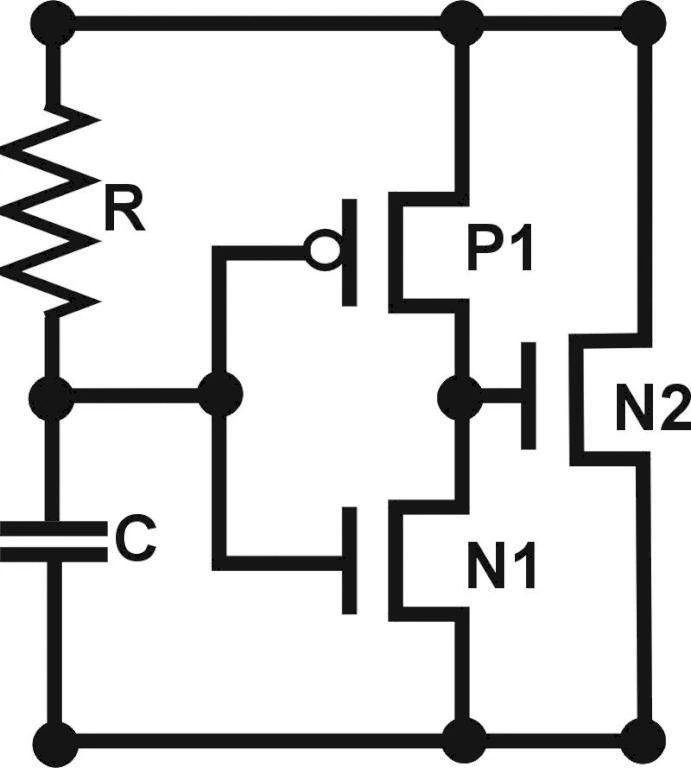

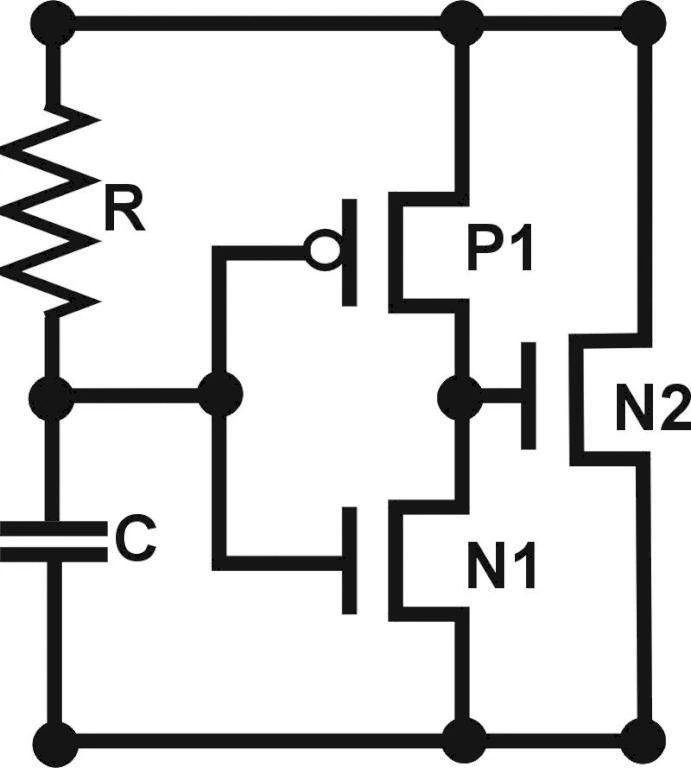

“有源 FET”是非常流行的 ESD 保护器件,通常用于低压应用。该名称指的是在有源工作模式下 ESD 电流通过 MOS 器件分流的事实。该模式仅在 ESD 条件下通过 ESD 事件检测器启用。该电路定时在 ESD 事件的整个持续时间(1-2 微秒)内保持导通状态。

在 CMOS 技术中,氧化物和漏极结共享相同的额定电压,通态是通过漏极与栅极的瞬态耦合来实现的。图 5 显示了该概念的基本实现。

对于高压器件(如前面提到的 DEMOS 和 LDMOS),漏极额定值可能远高于栅极额定值(例如,漏极额定值为 20V,而栅极额定值仅为 3.3V)。因此,如图所示的电路将无法工作,因为漏极和栅极基本上具有相同的电压,从而导致栅极可靠性问题(图 5)。

需要一种方法来分压焊盘电压以获得适当的栅极电压。这可以通过源跟随级来实现(图 6)。该方案允许典型的高压器件在正常的漏极和栅极工作额定值内工作。此外,与电路相比,它还具有两个显着优势(图 5):

电容要小得多,因为它驱动的晶体管要小得多。

开启/关闭时间常数是分开的,并且可以单独优化。

高压

可控硅整流器 (SCR)

可控硅(SCR)是pnpn结构。凭借嵌入该 pnpn 结构中的垂直 pnp 晶体管和横向 npn 晶体管的相互耦合,SCR 成为 ESD 功耗方面有效的器件。一旦两个双极晶体管之一开启,另一个双极晶体管也会开启,依此类推。

参考图 2,通过在漏极阱扩展内添加高掺杂 P 型扩散,将 SCR 集成到任何 DeMOS(或 LDMOS)中都非常简单。从图6中可以看出,形成了npn和pnp相互耦合的pnpn结构。此外,栅极的存在可用于进一步调整 HV-SCR ESD 特性。

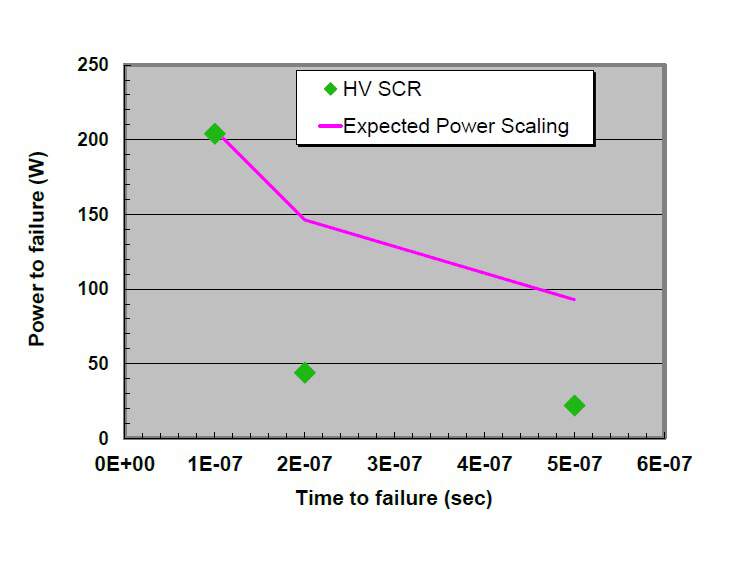

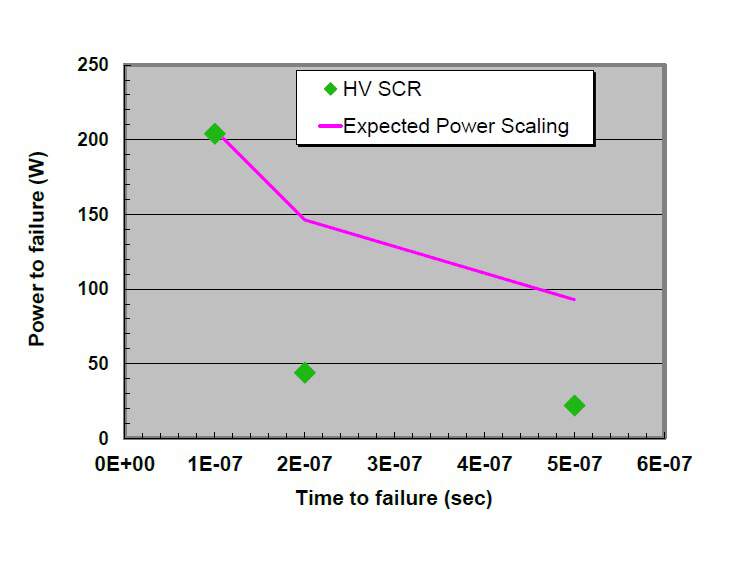

SCR 类型的根本问题是随着所施加 ESD 应力的脉冲宽度增加,它们保持功率缩放特性的能力 [2]。更具体地说,根据 SCR 在 100ns ESD 脉冲下消耗的功率,人们预计 [2] 在 200ns 和 500ns ESD 脉冲下会消耗一定的功率。

然而,200ns 和 500ns ESD 脉冲下的实际功耗远低于预期(图 8)。这是一个重大问题,特别是在 ESD 脉冲源自系统级事件的情况下,其中应力持续时间可能大大超过标准 HBM 事件的持续时间。

高压双极

正如高压 SCR 所强调的那样,高压双极器件也无法避免较差的缩放功率缩放特性。如图 9 所示,实际功耗从 100ns 开始就不遵循功率缩放定律。

除了与设计为 ESD 保护电路的高压双极器件相关的功率缩放问题外,还需要考虑与高压双极器件相关的另一个方面:由与相邻焊盘相连的 N 扩散形成的寄生双极器件。

参考图 10,焊盘(PAD1 和 PAD2)通常具有以公共接地 (GND) 为基准的 ESD 保护。如果发生从 PAD1 到 PAD2 的 ESD 事件,ESD 电流(图 10 中的红色实线)将从 ESD 保护 1 流经公共 GND 和 ESD 保护 2,到达 PAD2。随着 N 扩散与 PAD1 和 PAD2 相关,现在形成了寄生 npn 双极(公共 p 基板充当双极的基极),它可以在 ESD 事件期间传导电流,并终失效。

此配置的主要问题是由于 ESD 保护 2 中流动的 ESD 电流,寄生双极(公共接地)的基极具有升高的电势。这使得寄生双极非常容易被触发,因此,容易失败。

与 CMOS 技术不同,在模拟技术中,使用多个 N 型扩散来支持许多不同的额定电压和隔离技术是很常见的。因此,N 型扩散的任何排列都会在类似于图 10 所示的情况中产生寄生。考虑到发射极、集电极、基极类型的数量和几何效应,很可能在一个给定的技术。这对于 ESD 设计来说是相当具有挑战性的,因为 ESD 保护网络必须能够充分保护上述寄生效应。

ESD 资格挑战

“片上”系统级要求

为了保证 IC 制造过程中对 ESD 事件的鲁棒性,需要执行 HBM 和 CDM 测试。过去几年,出现了一种新趋势,要求在 IC 级提供系统级 ESD 保护。通常,系统级 ESD 保护是在系统级解决的,方法是在电路板上(靠近 ESD 应力源)放置专用瞬态电压抑制器 (TVS) 电路。这一趋势背后的基本原理是,如果单个 IC 具有 ESD 系统级鲁棒性,则可以消除 TVS(从而降低成本和系统设计复杂性)。

不讨论为什么这个原理有缺陷,这些要求对 IC 级 ESD 设计的影响是巨大的,不仅在 ESD 面积方面,而且在设计复杂性和所需的学习周期方面。

定制 ESD 级别要求

IC 级 ESD 稳健性的典型 ESD 级别要求是 2000V HBM 和 500V CDM。尽管已明确证明 1000V HBM 和 250V CDM 在当今的制造环境中可提供非常可靠的 ESD 设计,但某些客户可能需要在选定引脚上具有 >8KV HBM 性能,以处理未指定的系统级事件。这些要求的影响在面积和开发时间方面再次非常重要。

可持续发展战略

模拟技术组件产品组合的广度以及随后需要保护的大量应用并不适合满足所有要求的“单一 ESD 策略”。因此,模拟技术领域的 ESD 工程师正在研究所有 ESD 保护策略,仔细权衡利弊,以找到合适的解决方案。

有源 FET:它们在低压应用中非常有效且受欢迎。然而,对于高电压应用,低 FET 驱动电流和大面积的结合使其吸引力下降。

基于击穿的器件:它们依赖于寄生双极 npn 或 pnp。由于出色的面积/ESD 性能权衡,基于 Npn 的器件非常受欢迎。主要缺点是难以控制过程变化的性能。

SCR:这些解决方案在面积/ESD 性能方面是有效的,并且非常易于设计。然而,从 DRC-LVS 的角度来看,固有的闩锁风险和实施困难在一定程度上限制了它们的使用。

自我保护:该解决方案在大型输出驱动器的情况下非常有效,该驱动器也可以设计为承受 ESD 事件。缺点是需要在 IP 和 ESD 之间进行协同设计。