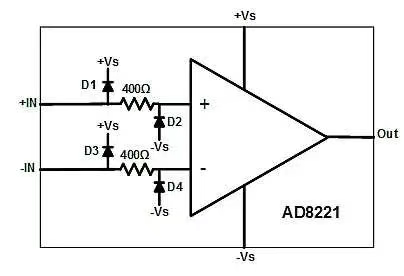

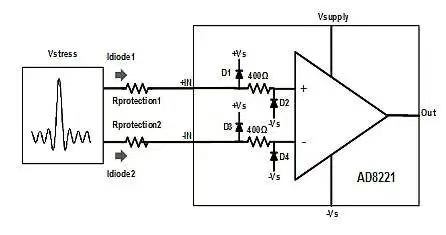

图 1 展示了在输入引脚和电源之间连接有二极管的放大器示例。在正常工作条件下,二极管处于反向偏置状态,但当输入电压上升到高于正电源电压或低于负电源电压时,二极管会变为正向偏置。此时,电流会通过放大器的输入流到相应的电源。在图 1 所示的电路中,当过压超过 +Vs 时,输入电流本身不会受到放大器本身的限制,需要以串联电阻器的形式进行外部电流限制。当电压低于 –Vs 时,400Ω 电阻会提供一定的电流限制,这在设计时应予以考虑。

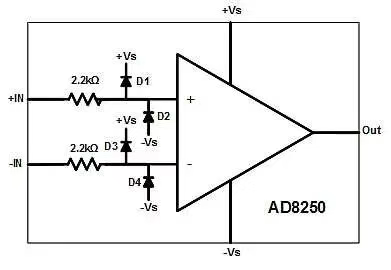

图 2 显示了一个具有类似二极管配置的放大器,但此电路中电流受到内部 2.2kΩ 串联电阻的限制。与图 1 所示电路的不同之处不仅在于限制电阻的值,而且 2.2kΩ 电阻可防止电压高于 +Vs。这体现了使用 ESD 二极管时必须充分理解的复杂性,以优化保护效果。

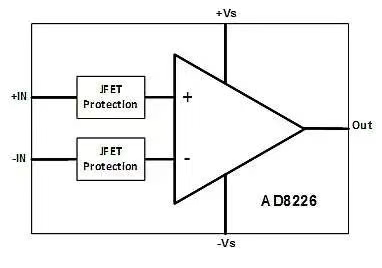

与图 1 和图 2 中的实施方式相比,限流 JFET 可在 IC 设计中用作二极管钳位的替代方案。图 3 展示了一个示例,当输入电压超过器件的指定工作范围时,JFET 用于保护器件。该器件通过 JFET 输入从相反的电源轨获得高达 40V 的固有保护。由于 JFET 会限制进入输入引脚的电流,所以 ESD 单元不能用作额外的过压保护。在需要高达 40V 的电压保护时,该器件的 JFET 保护提供了一个控制良好、可靠、完全指定的保护选项,这与使用 ESD 二极管进行保护形成对比,因为关于二极管电流限制的信息通常仅为典型信息,或者可能根本未指定。

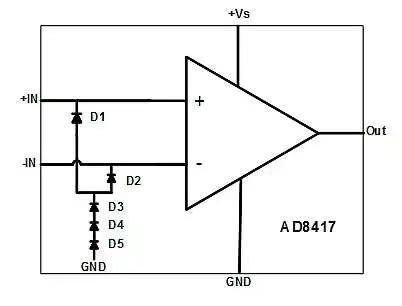

在允许输入电压超过电源电压或接地的应用中,可使用一组二极管来保护输入免受 ESD 事件的影响。图 4 显示了一个实施堆叠二极管保护方案的放大器。在此配置中,二极管串用于防止出现负瞬态。二极管串用于限制可用输入范围内的漏电流,但在超过负共模范围时提供保护。需要注意的是,的电流限制是二极管串的等效串联电阻。外部串联电阻可用于降低给定电压电平的输入电流。

当输入电压范围允许超过电源时,也会使用背对背二极管。图 5 显示了一个放大器,它采用背对背二极管为器件提供 ESD 保护,该器件允许使用 3.3V 电源提供高达 70V 的电压。D4 和 D5 是高压二极管,用于隔离输入引脚上可能存在的高压,D1 和 D2 用于在输入电压在正常工作范围内时防止漏电流。在这种配置中,不建议使用这些 ESD 单元进行过压保护,因为超过高压二极管的反向偏压很容易导致性损坏。

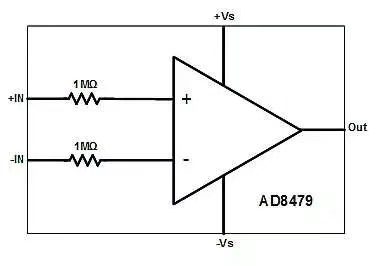

某些设备在前端不包括 ESD 设备。虽然很明显,如果 ESD 二极管不存在,设计人员就不能使用 ESD 二极管进行钳位,但在研究过压保护 (OVP) 选项时,提到这种架构是需要注意的情况。图 6 显示了一个仅使用大值电阻器来保护放大器的设备。

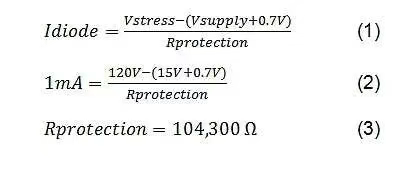

除了了解如何实施 ESD 单元之外,了解如何利用其结构进行保护也很重要。在典型应用中,串联电阻用于限制指定电压范围内的电流。当放大器按图 7 所示配置或输入受电源二极管保护时,输入电流将使用以下公式进行限制。

用于公式 1 的假设是 Vstress>Vsupply。如果不是这种情况,则应测量更的二极管电压并将其用于计算,而不是 0.7V 近似值。下面是一个计算示例,用于保护使用 +/-15V 电源的放大器,免受高达 +/-120V 的输入应力,同时将输入电流限制为 1mA。使用等式 1,我们可以使用这些输入来计算所需的保护电阻。鉴于这些要求,Rprotection >105 kΩ 会将二极管电流限制为 <1 mA。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。