秒速度低于 1 至 3 Gbits/秒范围。随着背板和网络接口进入该速度范围,那些在 10 Gb/秒领域开始首次设计的人可能不得不面对新的现实,这些现实将主导信号质量问题。

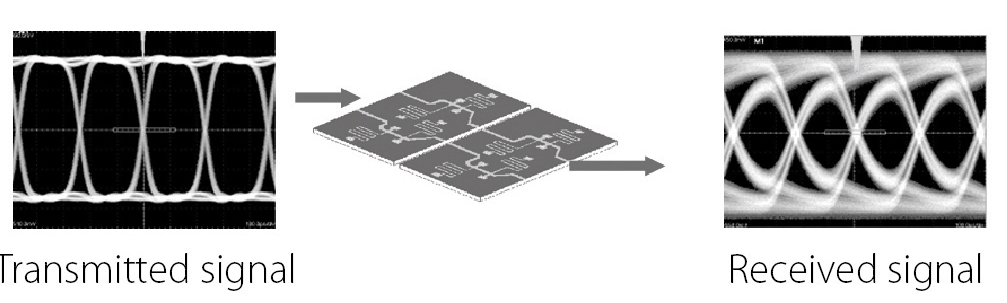

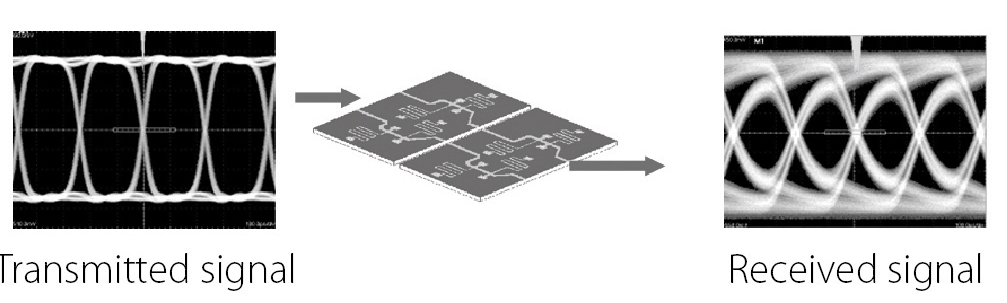

不仅在单个器件层面,而且在电路板走线层面都会遇到不连续性,这些都会影响电路板布局和基板材料(例如 FR4)的选择。形状正确、“干净”的传输信号在接收器处看起来会非常不同,如图 1 中的眼图所示。

10 Gbits/秒及以上信号完整性的问题和陷阱

图 1:眼图清楚地显示了发送信号形状和接收信号形状之间的信号衰减,这种情况发生在信号路径属性上。

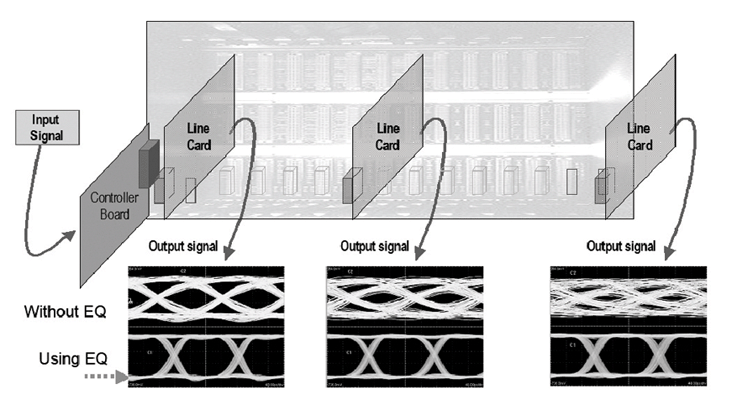

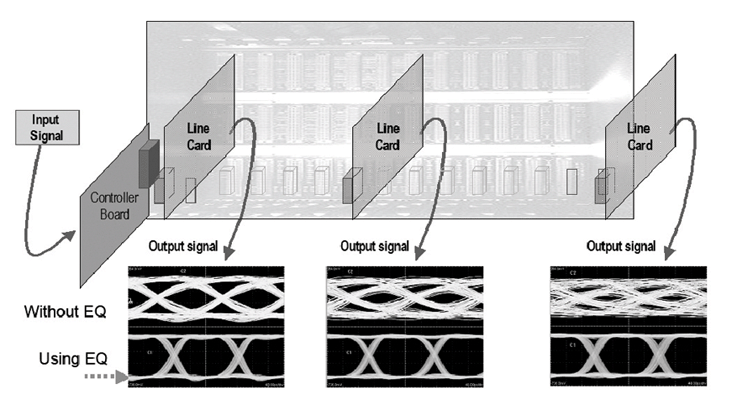

要表征 10 Gbits/sec 及以上速率下的线卡和背板的信号完整性问题,需要同时在板级和设备级可视化设计,如图 2 所示。

图 2:适当的均衡可以成功恢复信号路径连续阶段发生的退化累积。

事实上,尽管系统开发人员必须跟踪高速设计中使用的各个器件的均衡和纠错功能,但印刷电路板 (PCB) 设计人员仍被称为 10G 设计方法的“看门人”。当同时在板级和器件级考虑该任务时,会出现一些潜在信号完整性问题的常见

PCB 布局: 物理设计的特征(例如通孔存根的使用)可能会对每秒数十吉比特运行的数据通道的完整性产生重大影响。先进设计中使用的加扰方法可能会加剧交流耦合的困难。随着标准已从 8B/10B 编码转变为 66B/64B,这种加扰问题的解决难度更大。

不良的过孔布局和交流耦合的结合可能会导致信号出现明显的基线漂移,而这种漂移无法通过输入均衡来缓解。相反,必须在设备和电路板级别实施设计规范,并实时监控眼图。

这并不是担心高速设计的原因。行为的实时监控是确定性的,并且可以使用以合理成本提供的测试设备来监控信号。但必须从高速设计的早期阶段就考虑信号质量的限制。例如,对过孔存根进行背钻,通过将迹线彼此间隔至少三个电介质厚度来隔离迹线,使用大型交流耦合

电容器来传递低频内容。

平面不连续性: 可以通过正确的信号端接和简单直接的电路板布局来处理不连续性。当不连续性通过使用具有许多过孔存根的多层板、具有多个过孔的表面贴装元件以及具有快速传输边缘速率的所有类型(特别是表面贴装)的器件而在整个单一设计中传播时,就会出现问题。由于沿信号走线的过孔数量较多,而且即使在开放区域,接地过孔的分配也很稀疏,因此接地过孔的间距应适当,以防止出现波导模式。

边缘速率设计技术: 这是与设计中使用的特定器件相关的问题,可能会对板级布局产生影响。快速输出边沿和上升时间可以消除或减少对预加重或去加重的需要,并且没有预加重或去加重的设计可以提供更少的串扰和更低的功耗。对边缘速率的考虑使我们能够在设备级别更适当地考虑信号完整性问题。

发送均衡: 可以通过使用时钟驱动器在数字域中执行预加重、去加重和预补偿,或者以模拟方式使用基于时域的多重衰减

滤波器。

接收均衡: 多级模拟输入信号均衡可能比简单的单级设计更复杂,但高频设计需要非线性输入均衡。此类设计中的仔细规划可以允许使用低成本 PCB 材料,例如 FR4。

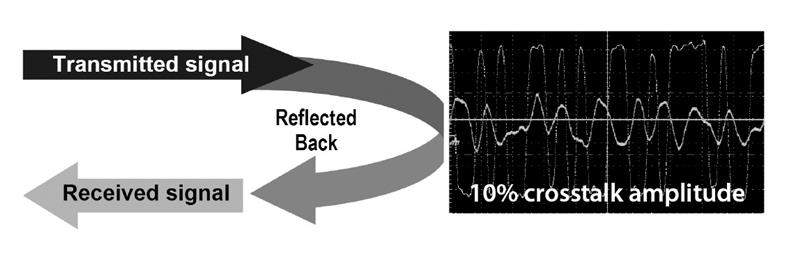

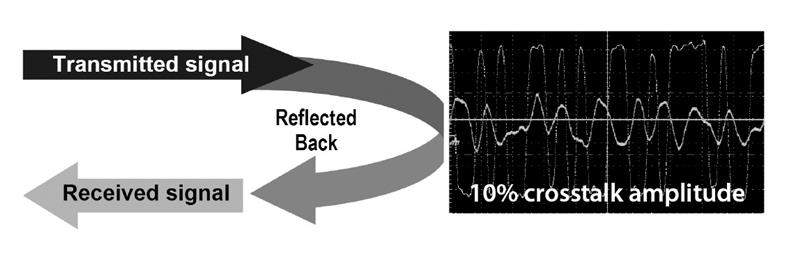

发送和接收链中的均衡可以利用重定时器信号模拟均衡来补偿线性高频损耗,并且重定时器电路和 IC 中的数字均

衡器或决策反馈均衡器 (DFE) 的可用性可以帮助对抗串扰和反射,图3。

图 3:即使是少量的串扰也会因反射而影响信号完整性。

随着背板设计人员从单通道转向符合10GBASE-KR标准的多10Gbit串行通道,以及线卡接口开发人员转向QSFP+、CFP、CXP等新兴收发器模块,重定时器芯片的使用几乎在很多情况下肯定需要。

器件和电路板级的波形分析: 随着高速设计中越来越多的器件使用均衡,人们通常不认识到的一个因素是波形分析变得更加困难。 100 Mbits/sec 和 1 Gbits/sec 设计中遇到的干净且开放的眼图与速度高于 10 Gbits/sec 的噪声几乎无法区分。许多半导体供应商正在转向高速线卡的嵌入式探头和测试点技术,的设计提供可从芯片级访问的完整嵌入式波形分析。

除了在台架测试中实时监控眼图之外,更广泛地使用嵌入式分析功能还可以带来额外的好处。转向具有嵌入式测试功能的重定时器设备可以远程连续监控网络节点,以实现自动保护切换等功能,本质上是在系统内的任何地方放置

示波器。这允许监视器的专门、间接使用,用于子通道相位调制、信号鉴定和误锁检测等属性。

随着非线性均衡方法和带 DFE 的重定时器的使用变得越来越普遍,并且嵌入式波形分析的添加不再只是测试台的好奇心,设计人员可能会发现 10 Gbit 时代的信号完整性变得相对容易解决。由于 10 Gbits/秒的信道带宽正在成为未来 40 Gbit 和 100 Gbit 系统的标准设计,因此今天采用的 10 Gbits/秒系统的设计方法将具有适用于几代的传统。

然而,需要重申的是,当通道速度超过 3 Gbits/sec 时,设计电路板走线的旧方法(例如使用单级线性均衡以及尝试在没有嵌入式探头的情况下观察波形)几乎无法满足要求,以及向 10 Gbits/秒及以上的转变。