数模

转换器 (DAC) 的静态精度可以用三种基本类型的误差来描述:偏移、增益误差和非线性。线性误差是三者中难处理的,因为在许多应用中,用户可以消除偏移和增益误差,或者通过在系统设计中构建端点自动校准来补偿它们。然而,线性误差需要更复杂的校正。

DAC(图 1)将数字输入代码转换为成比例的模拟输出信号,该信号可以是电流或电压。 DAC 的分辨率是指 DAC 能够产生的独特输出电平的数量。例如,分辨率为 8 位的 DAC 将能够在其输出处产生 2× 8 (256) 个不同的输出电平。理想情况下,每个数字代码提供相同的模拟步骤;然而,由于非理想性,实际上不可能。

图 1 : 8 位 DAC 符号和作用

DAC 的线性度

在研究如何提高 DAC 的积分非线性 (INL) 之前,回顾一下我们如何确定其线性度,如图2所示。在 DAC 中,我们主要关注其线性度的两种测量:微分非线性 (DNL) 和积分非线性 (INL)。

DNL 是相邻输入代码之间的实际模拟输出步长与理想步长值的偏差。 INL 是传递函数中任意点实际输出电平与其理想值的偏差。理想值是 DAC 的实际零值和满量程之间绘制的直线。

通过增益校正改善 DAC 积分非线性

图 2 : DAC 线性误差、DNL 和 INL

传统的端点校准技术用于消除 DAC 中的增益误差。然而,由于硅中存在各种系统非理想性,增益误差在 DAC 的满量程范围内通常不是线性的。这些系统模式可能会导致单向梯度,从而导致 INL 性能不佳。

造成系统模式的主要非理想性如下:

边缘效应,例如扩散长度 (LOD)

掺杂梯度

氧化物厚度梯度导致芯片上的阈值偏移

热梯度

供电线路中的电压降

因此,端点校准技术不足以完全消除增益误差,并且可能导致 INL 性能不佳。需要输出精度的应用可能需要低得多的 INL。

固件技术

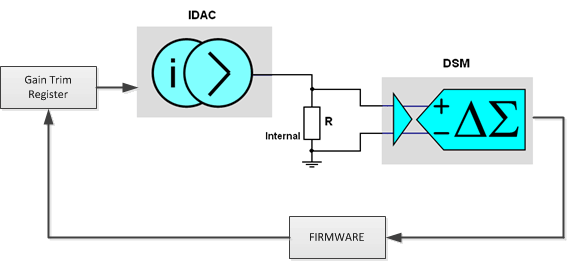

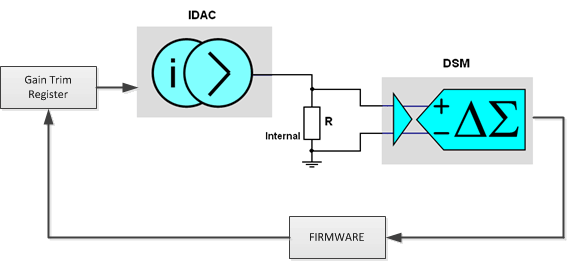

提高 INL 性能的一种方法是使用固件技术。该技术利用 SoC 的优势在系统中构建两点自动校准。对于本示例,我们将使用 PSoC 3 系列,具有多达四个多范围 8 位电压/电流 DAC,INL 约为 1.5 LSB。片上 20 位 Delta-Sigma

模数转换器 (ADC) 在 12 位模式下工作时的 INL 小于 1 LSB。这足以校准 8 位 DAC。固件需要完成 DAC 输出和 ADC 之间的反馈环路(图 3)。

图 3 :具有 ADC 反馈的电流输出 DAC (IDAC)

INL 通常倾向于在整个范围的中间达到其值,如图4所示。如果我们能够降低这个峰值,我们将显着改善 INL。这一观察结果导致我们使用两点校准而不是端点或单点校准技术,这些技术本身可能不足以完全消除增益误差。

图 4 : 不同增益区域的 DAC 线性度

个校准点将用于校准整个范围的前半部分(公式 1)。

同样,第二个校准点是校准整个范围的后半部分(公式 2)。

该算法如图 5所示,工作原理如下。初,在数字输入 DAC 值的中点和端点处计算并保存两个增益校正值。这是使用ADC。因此,我们只牺牲测量和计算时间来进行校准。

图5 : 两点增益校正算法流程图

在正常操作期间,如果小于中点的数字代码被传递到DAC,则在转换之前使用增益校正值对其进行校准。如果大于中点的数字代码被传递到DAC,则在转换之前使用第二增益校正值对其进行校准。

校准将通过更新增益调整寄存器来即时完成,如图 3 所示。如果 SoC 上可以使用直接

存储器访问 (DMA) 模块来更快地更新寄存器,则将使用该模块。

更改整个范围中间的增益校正值将产生微调偏移(公式 3)。

通过增益校正改善 DAC 积分非线性

该微调偏移需要在范围的后半部分进行补偿,如图 5 的算法所示。

结果

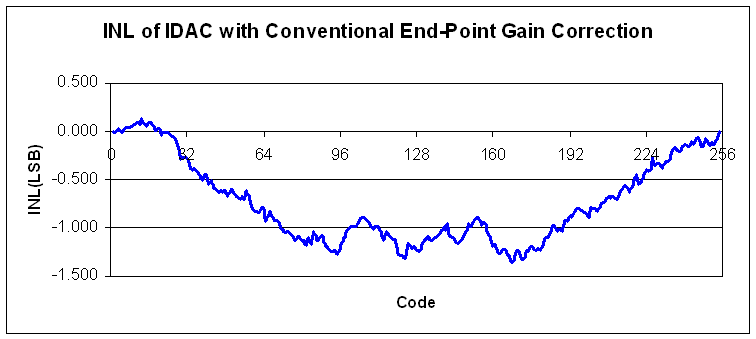

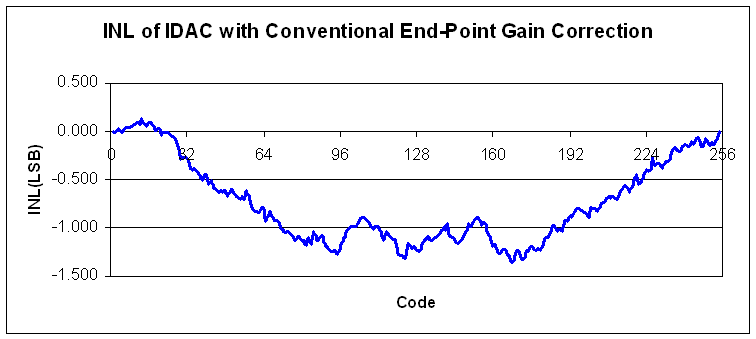

为了进行比较,在应用所提出的算法之前,首先测量具有传统端点校准的 8 位电流 DAC (IDAC) 的 INL 性能。如图 6所示,INL 约为1.5LSB。

图 6 : 采用传统端点增益校正的 IDAC 的 INL

实施所提出的算法后,INL 现在降低至0.8LSB, 图 7。

图 7 : 具有两点增益校正的 IDAC 的 INL