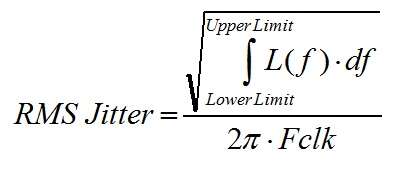

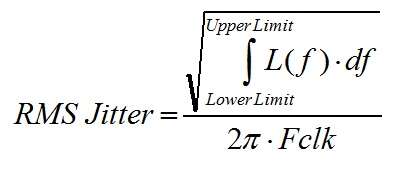

电源噪声会降低时钟器件的随机抖动性能。随机抖动根据相位噪声 (L)、偏移频率 (f) 和时钟频率 (Fclk) 计算得出(公式 1):

公式1

通常,L(f) 是时钟的相位噪声,但也可能意味着由于电源噪声而导致时钟上的杂散和相位噪声。时钟频率附近的噪声和杂散会导致抖动恶化。例如,如果 100 MHz 时钟上存在 10 kHz 电源噪声,则导致抖动恶化的不是 10 kHz 杂散,而是 100 MHz +/- 10 kHz 处的杂散。

要了解电源噪声的一般影响,首先使用公式 2 检查正弦噪声源的影响:

公式 2

一旦了解了电源噪声对任意频率 f 的影响,就可以将其扩展到任何电源噪声频谱。通过了解噪声源(公式 2)如何影响时钟器件对噪声敏感的模块,以及锁相环 (PLL) 如何对它们进行整形,就可以发现对抖动产生的影响。

电源噪声对

振荡器的影响

为了讨论电源噪声,可以考虑 VCO、VCXO、XO、OCXO 和 TCXO 等振荡器。它们的电源噪声灵敏度可以用电源推动常数 KPUSH 来表征,即电源电压给定变化的频率。

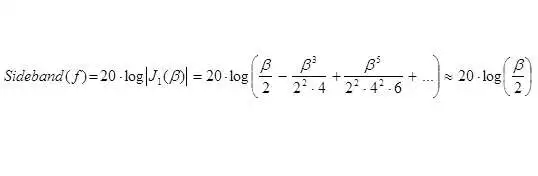

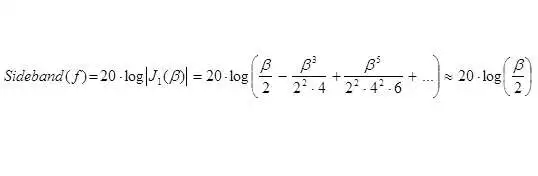

公式 2 中的噪声源产生频率等于 Fclk +/- f 的边带。这些边带的幅度可以使用公式 3 计算。

公式 3

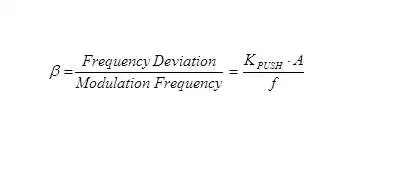

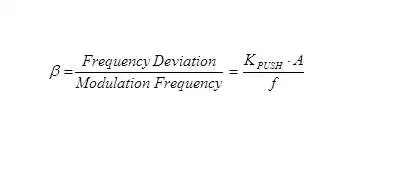

是调制指数,由传统 FM 调制理论计算得出(公式 4)。

信号链基础知识#71:电源噪声如何影响时钟设备

公式4

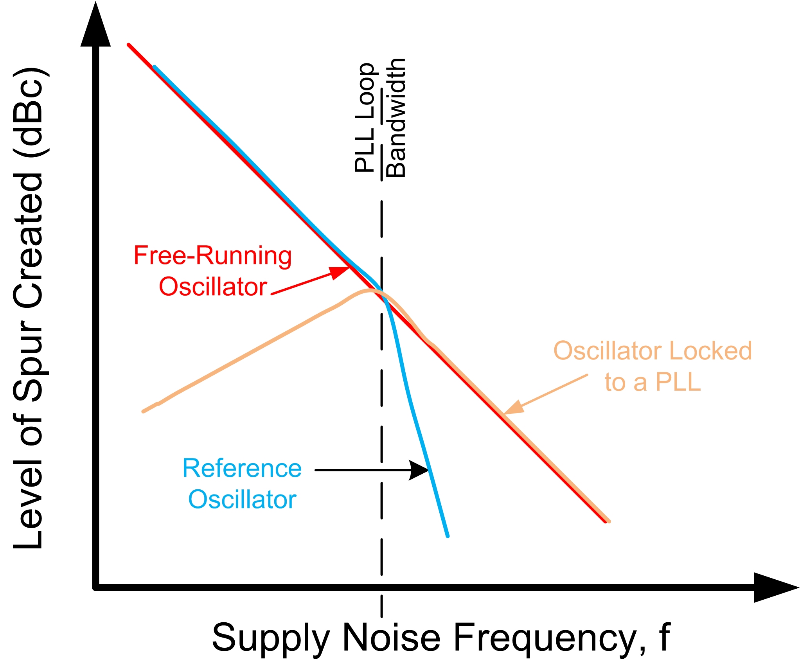

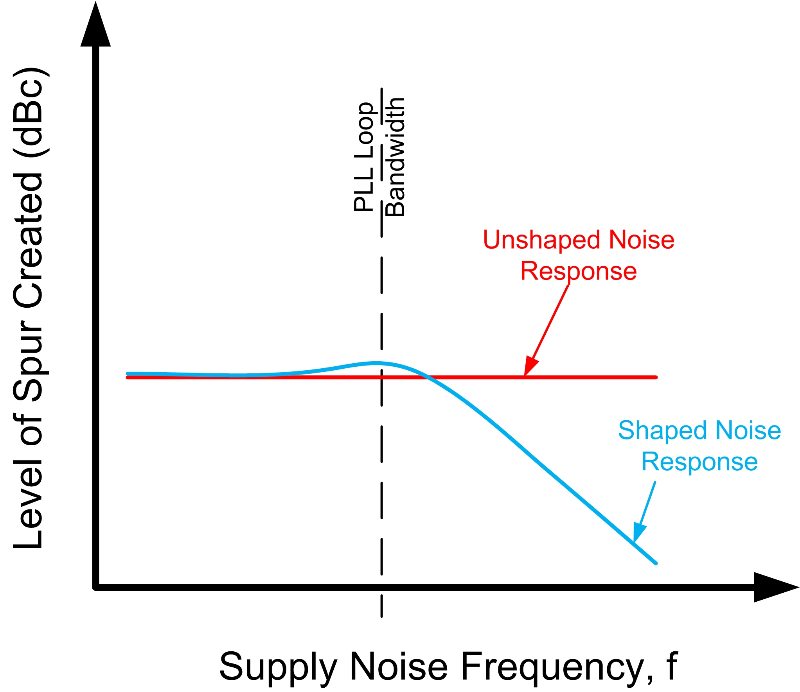

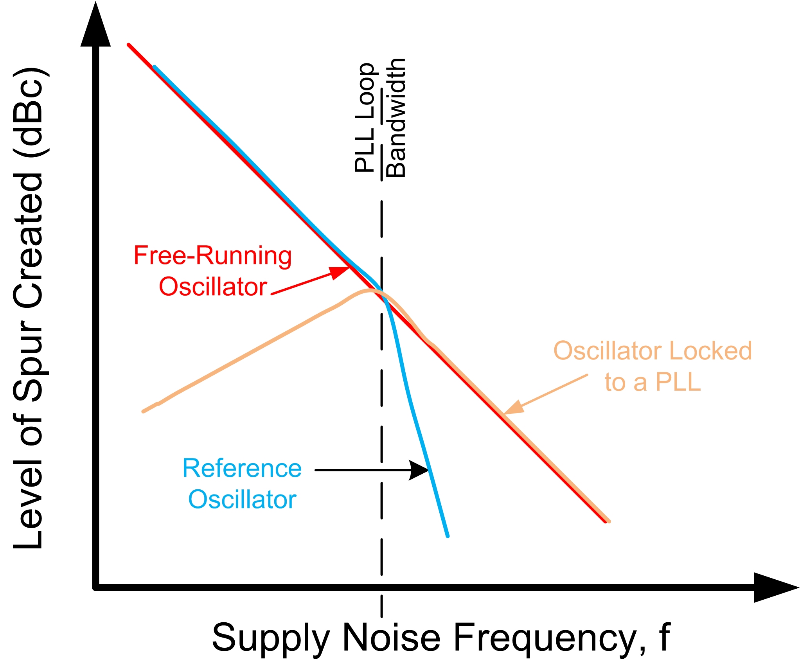

根据振荡器是自由运行、驱动 PLL 还是由 PLL 驱动,噪声响应会有所不同(图 1)。

信号链基础知识#71:电源噪声如何影响时钟设备

图 1. PLL 系统中振荡器的电源噪声响应。

图 1 显示低频电源噪声对振荡器相位噪声的影响为严重。如果振荡器被锁定到 PLL,则增加环路带宽有助于抑制这种低频噪声。如果使用振荡器作为参考,减小环路带宽有助于降低高频噪声。无论哪种情况,更好的电源滤波(尤其是在低频下)都至关重要。真正的低噪声低压差 (LDO)

稳压器非常适合此目的。

电源噪声对时钟设备其他模块的影响

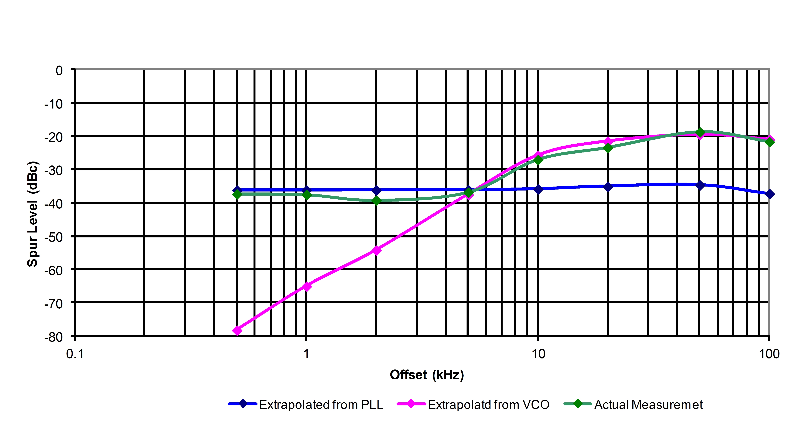

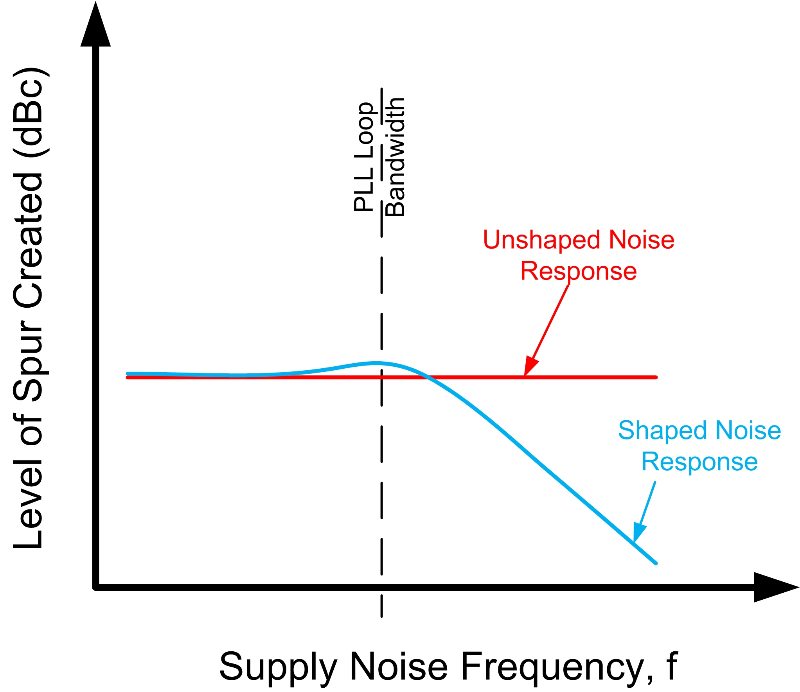

对于振荡器以外的模块,电源噪声响应在频率范围内往往更加平坦(在 PLL 整形之前)。电源噪声影响时钟器件的一种方式是电荷泵电源引脚和噪声响应(图 2)。

图 2. 电源噪声形状对 PLL 噪声的影响。

对于输出

缓冲器,电源噪声可能来自电源引脚和上拉或下拉电阻(如 LVPECL 发射极电阻)。对于不同频率的多个输出,旁路

电容器并不总是有用,因为一个输出电源引脚产生的噪声可以通过这些电容器耦合到另一引脚。

例子

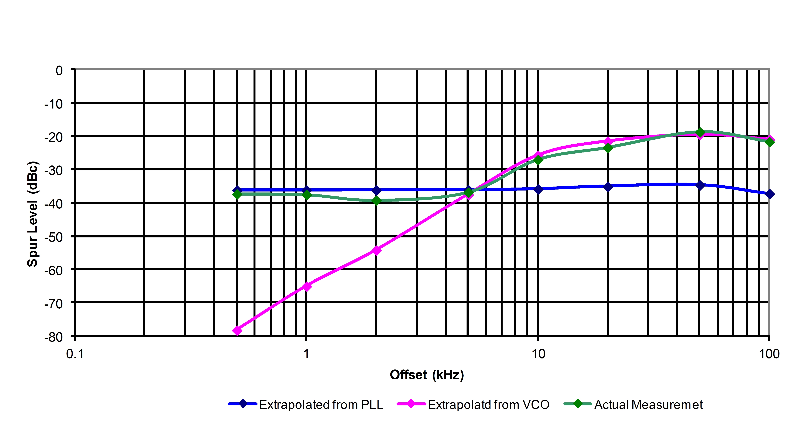

图 3 是通过首先测量带宽非常窄的 25 mV 信号的电源噪声影响来推断 650 kHz/V 的推动常数而创建的。接下来,我们使用宽环路带宽来测量 PLL 电荷泵。,我们使用约 50 kHz 的环路带宽来组合这些结果。

信号链基础知识#71:电源噪声如何影响时钟设备

图 3. 测得的电源噪声对 PLL 和 VCO 系统的影响。

概括

通过了解任意频率的电源噪声如何影响时钟器件的每个模块,可以找到任何抖动积分带宽、器件配置或电源噪声频谱引起的抖动。