高速 DAC 有两种类型:内插式和非内插式(直接)。 信号链基础知识 #55(参考资料 2 )中描述的插值 DAC通常包含数字信号处理功能,例如插值、数字正交调制和内部锁相环 (PLL)。直接 DAC 只是将数字值转换为模拟输出。

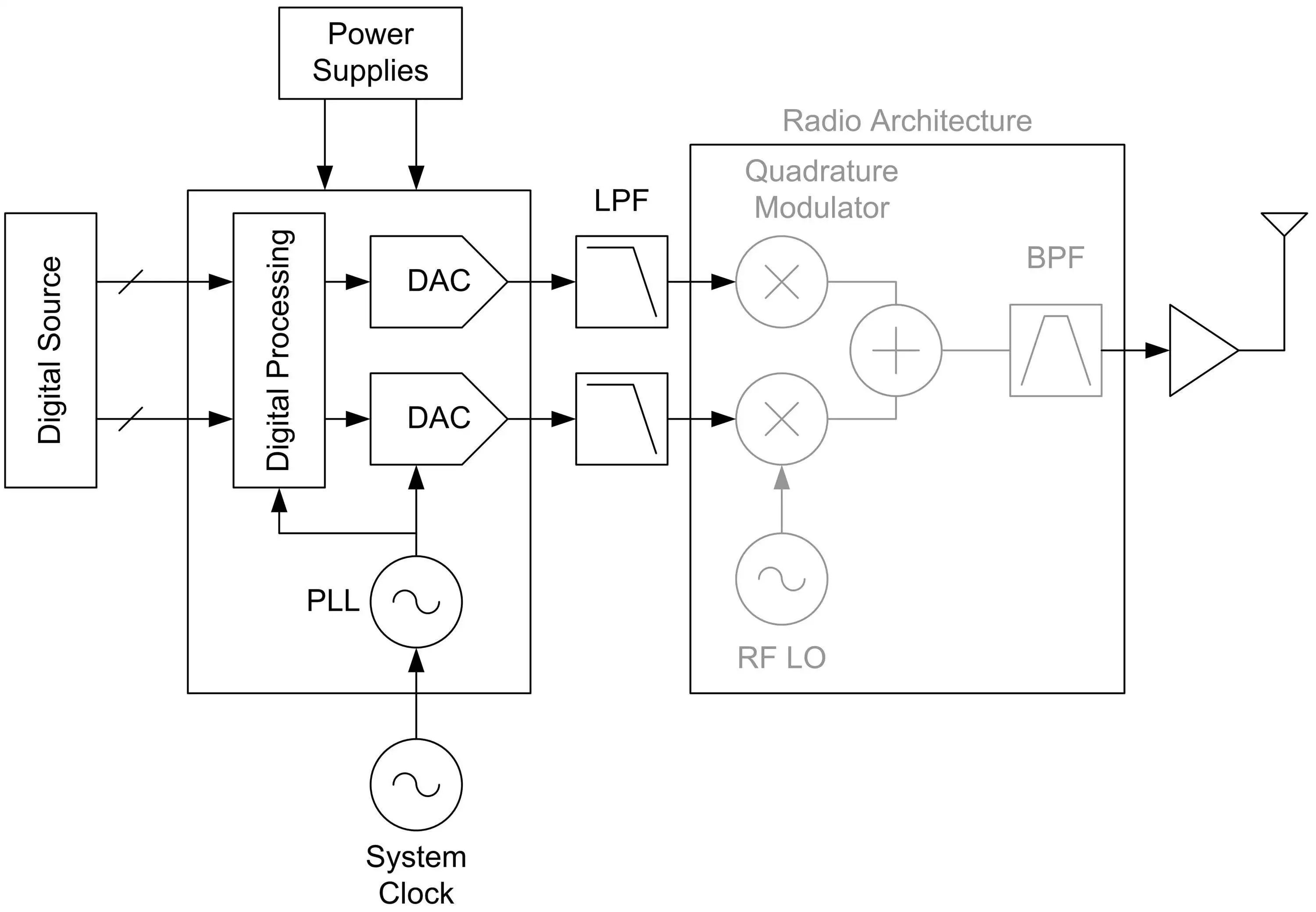

图 1 显示了无线电应用中的 DAC 信号链。 DAC 产生的杂散信号有多种潜在来源,每种来源都有不同的特征:

1) 数字接口

2) 输入时钟

3) 锁相环

4)

电源 5) 数字饱和

6) 输出端接不当

图 1 :典型的高速 DAC 信号链。

DAC 的特点是具有连续波 (CW) 或调制信号输出(通常是 3G 或 4G 通信信号,如 WCDMA 或 LTE)。数据表包含表中列出的交流规格以及输出频谱图。与频谱图进行比较可以为调试系统问题提供多的信息,因为每种问题类型都有不同的频率特性。

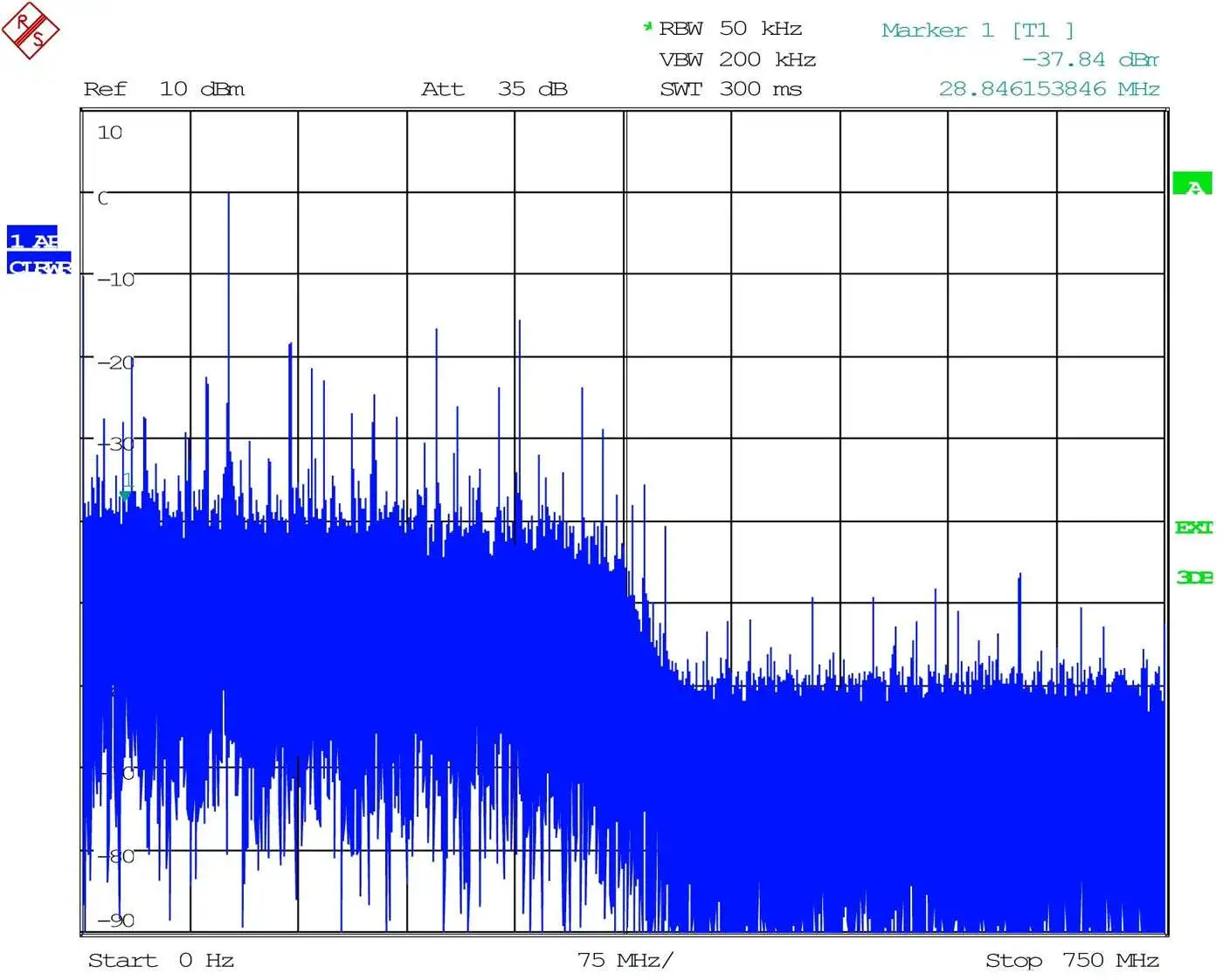

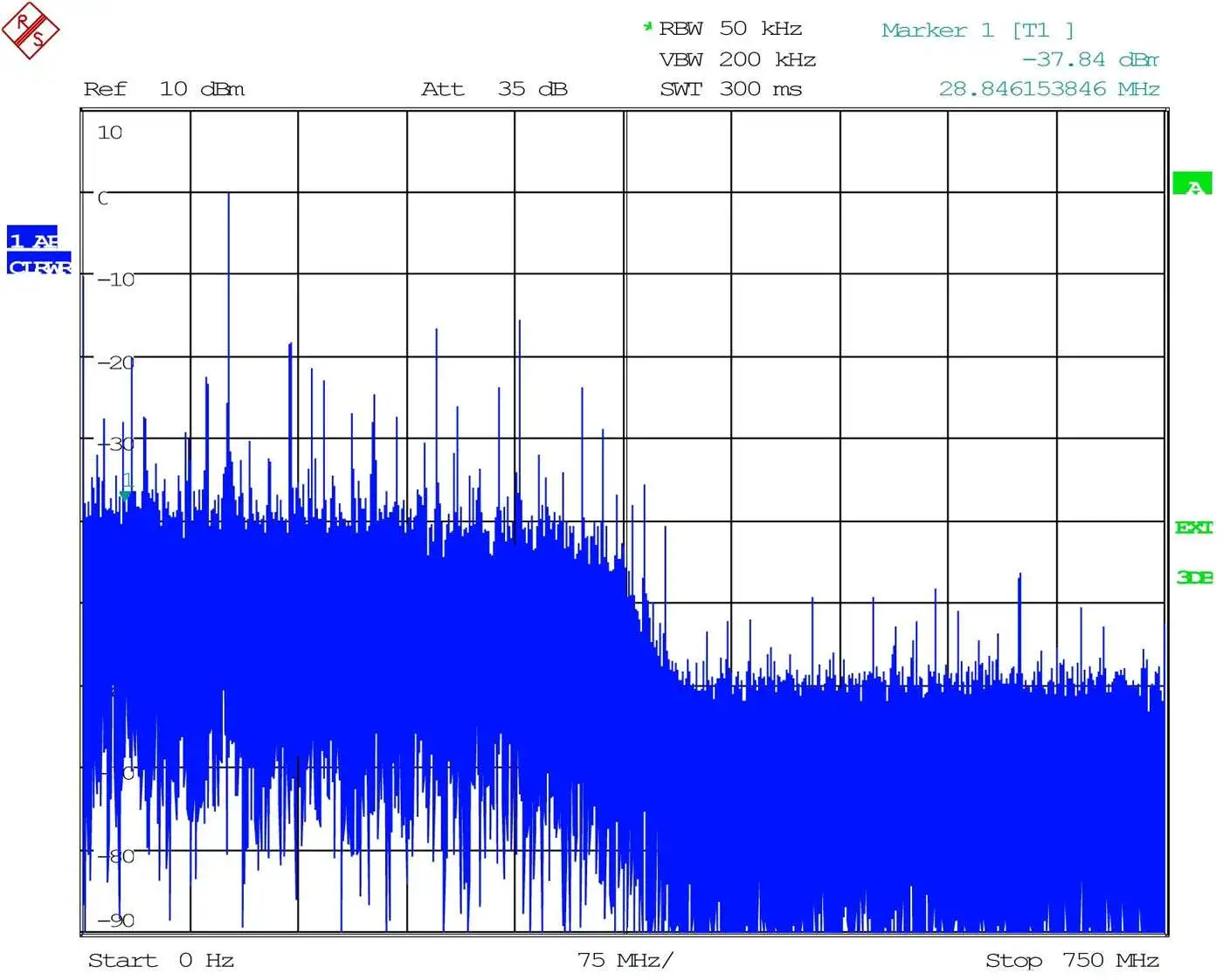

要调试高速 DAC,首先要验证无错误的数据输入。输入接口问题很常见,会导致误码,从而产生宽带噪声。在直接 DAC 中,这会导致 sin(x)/x 频率响应后本底噪声升高(图 2)。在插值 DAC 中,噪声频谱由内部数字插值

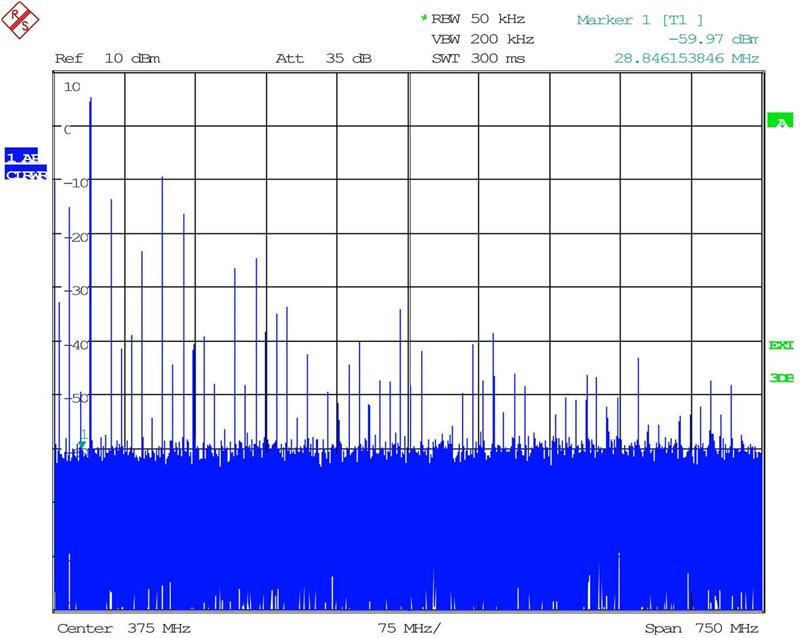

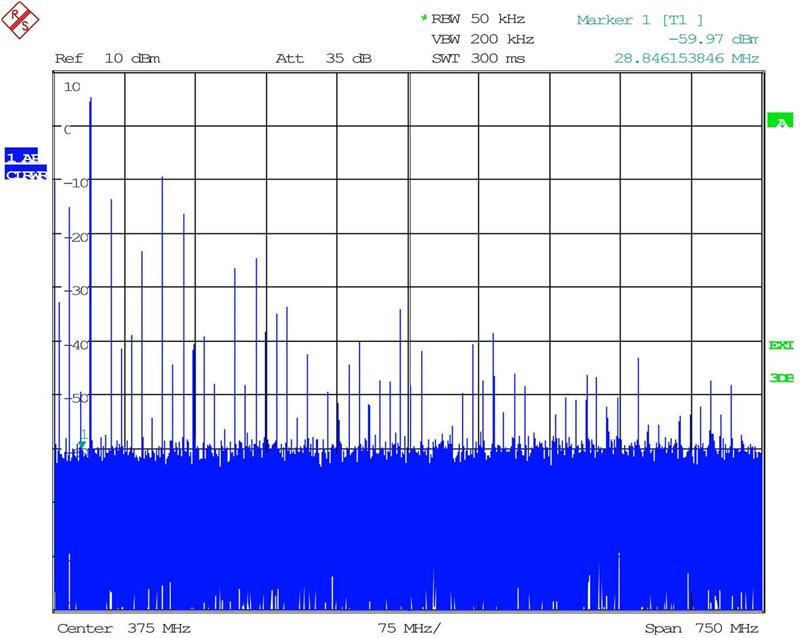

滤波器整形。这给出了与滤波器频率响应相匹配的独特输出频谱(图 3)。

图 2 :具有接口错误的直接 DAC 的输出频谱。

图 3 :具有接口误差的内插 DAC 的输出频谱。

TI 的 DAC34SH84(四通道、16 位、1.5 GSPS)等 DAC 包含多种可简化设计、验证和监控输入接口的功能。 DAC 包括时钟和数据之间的可编程偏移,增量约为 50 ps,以降低输入时序要求。为了进行验证,可以使用来自数字源的测试模式来识别特定的错误位。,该接口包括一个奇偶校验位,用于在操作期间连续监控接口。

时钟杂散是另一个常见的问题根源。由于 DAC 采样过程的作用类似于混频器,因此时钟输入上的毛刺会导致 DAC 输出上的毛刺。由于时钟杂散而导致 DAC 输出端杂散信号的频率随输入频率变化 1:1。

通过生成音调、记录杂散频率、将音调移动少量(例如 100 kHz),然后测量频移,容易看出这一点。

开关稳压器可能会导致时钟杂散与音调偏移几百 kHz。

另一个常见的时钟问题是内部 PLL 设置不当,导致 PLL 未锁定或相位噪声升高。

非线性失真会产生输出信号谐波。由于 DAC 的采样特性,在高于个奈奎斯特区域 (0 – f SAMPLE /2) 的频率处生成的谐波会折回 DAC 输出处的奈奎斯特区域。虽然杂散频率可以轻松计算,但您可以通过观察输出和输入频率之间的变化来识别谐波。输出频率的谐波变化如下:

f输出 = ±N × ??f输入

其中,Δf IN 是输入频率的变化,N 是谐波次数,Δf OUT 是输出频率的变化。

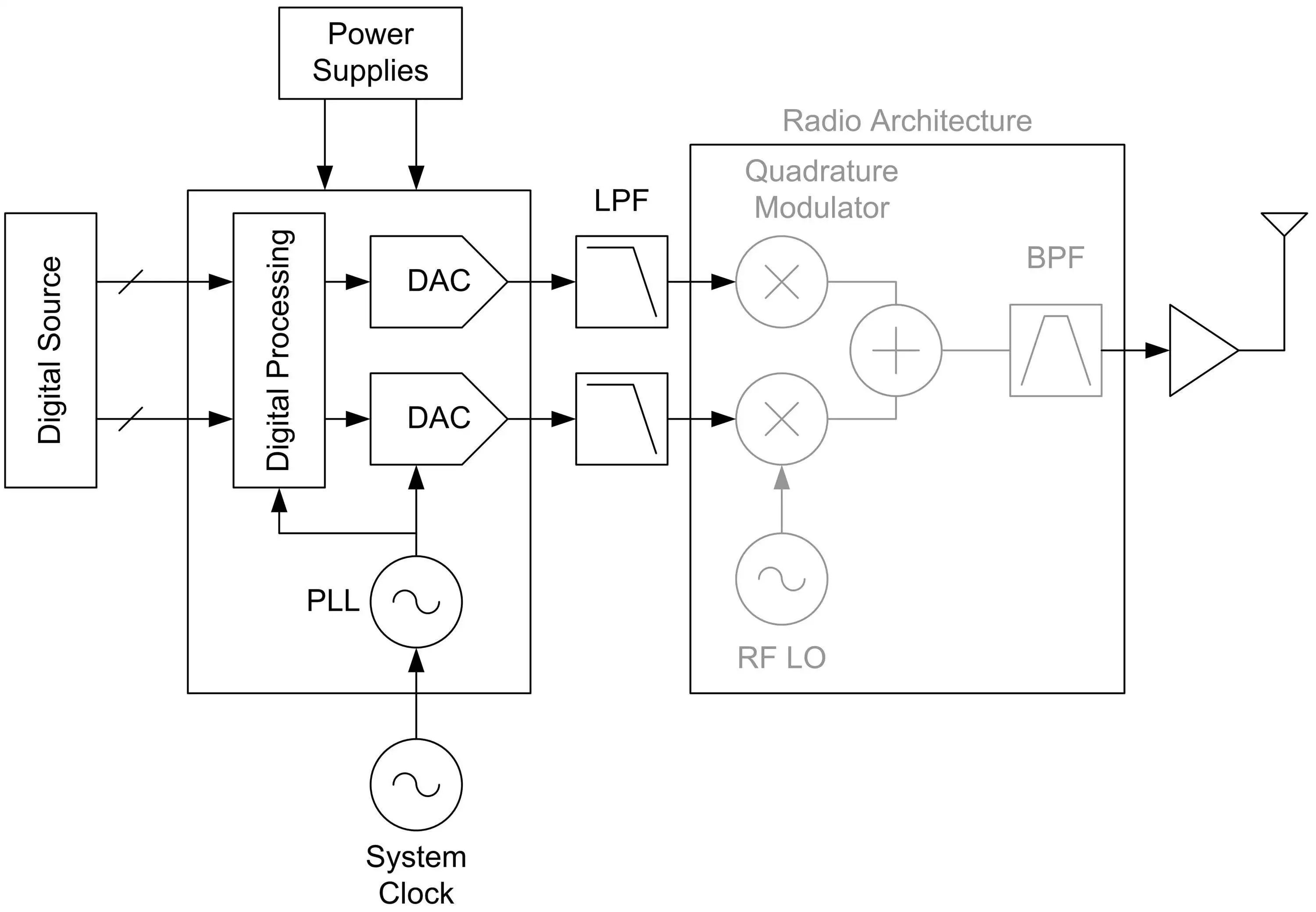

非线性失真的两个常见原因是数字饱和和不正确的输出端接。内插 DAC 通常具有具有潜在增益的信号处理模块,从而导致信号削波。削波会产生大量谐波(图 4)。

图 4 :具有数字饱和的 DAC 输出频谱。

在高速 DAC 中,输出电流由终端负载转换为电压。数据表包含输出合规电压的规范,这是 DAC 输出引脚可接受的电压范围。如果输出负载阻抗太高,则可能会超出合规电压规格,从而增加失真。请注意,如果例如它包括模拟滤波器并且临界阻抗处于预期工作频率,则阻抗可能与频率相关。