绘制漏极电流与漏极电压的关系图

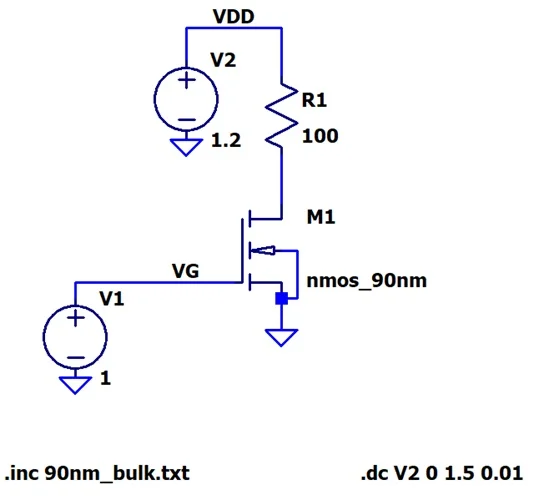

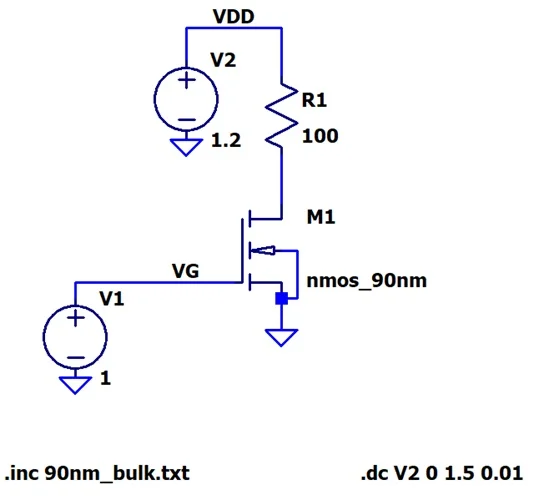

我们首先绘制漏极电流 ( I D ) 与漏源电压 ( V DS ) 的基本图。为此,我们将栅极电压设置为远高于阈值电压的固定值,然后执行直流扫描模拟,其中V DD的值逐渐增加。图 1 显示了我们将使用的原理图。

LTspice N

MOS 示意图,用于生成漏极电流与漏极电压的关系曲线。

图 1.基本 NMOS

晶体管的 LTspice 示意图。我们将使用它来生成漏极电流与漏极电压的关系曲线。

1 V 的栅极-源极电压 ( V GS ) 远高于我们在上一篇文章中通过模拟得出的阈值电压 320 mV。同时,图 1 右下角的.dc模拟命令告诉 LTspice 做两件事:

将 V2 源 ( V DD ) 从 0 V 以 0.01 V 的增量增加至 1.5 V。

使用这一系列V DD值作为独立变量。

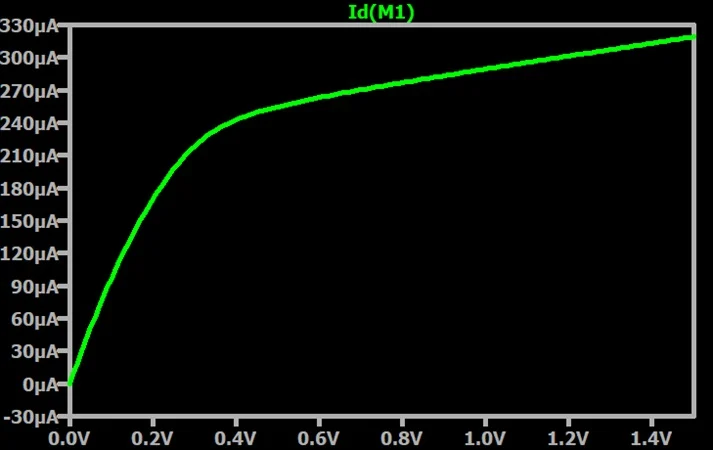

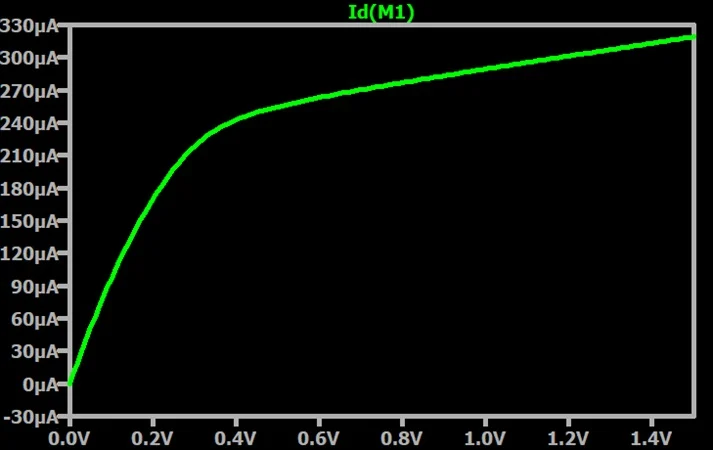

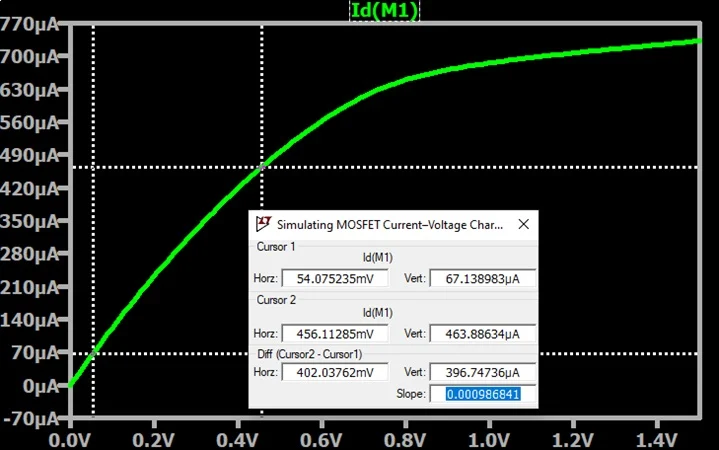

我们的模拟结果可以在图2中看到。

图 1 中 NMOS 晶体管的漏极电流与漏极电压的关系。

图 2.我们初始的漏极电流与漏源电压的关系图。

栅极电压足够高,可以实现导通,因此只要V DS超过零,电流就会开始流动。漏极电压较低时,漏极电流会随着V DS的线性增加而线性增加。但是,漏极电流在约 0.4 V 时开始趋于平稳,此后增加速度会更慢。从图中斜率较高的部分到斜率较低的部分的转变对应于 FET 的线性区域到饱和区域的转变。

当漏极电压较低时,栅极电压会打开从漏极延伸到源极的通道,电流会更自由地流过 FET 的通道。当漏极电压接近过驱动电压时,漏极处的通道会被夹断,电流不再像以前那样自由流动。过驱动电压等于栅极电压减去阈值电压。

测量线性区域的电阻

线性区域中的 NMOS 表现得像一个压控电阻。这就是该区域名称的由来——当电流流过

普通电阻时,电压和电流之间的关系是线性的。如果我们看一下欧姆定律,这一点就很明显了:

V=

IR 如果我们用高中代数中用过的字母替换V、I和R ,欧姆定律就变成:

Y=mx

在哪里:

y,纵轴,表示电压

x,横轴,是电流

m,绘制线的斜率,表示阻力。

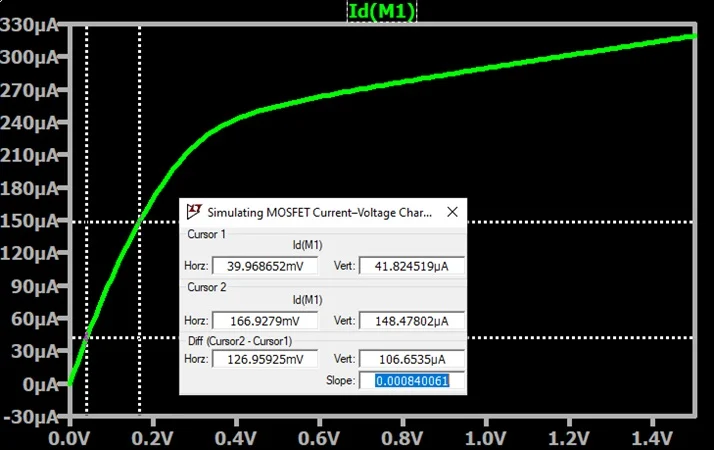

要确定此 NMOS 晶体管在线性区域中的电阻,我们只需找到m。由于我们在图 2 中绘制了漏极电流和漏极电压之间的关系,因此我们已经完成了部分工作。但是,我们在 y 轴上绘制了电流,在 x 轴上绘制了电压——要使V = IR起作用,电压必须是y值,电流必须是x 。m不是图 2 中直线的斜率,而是斜率的倒数。

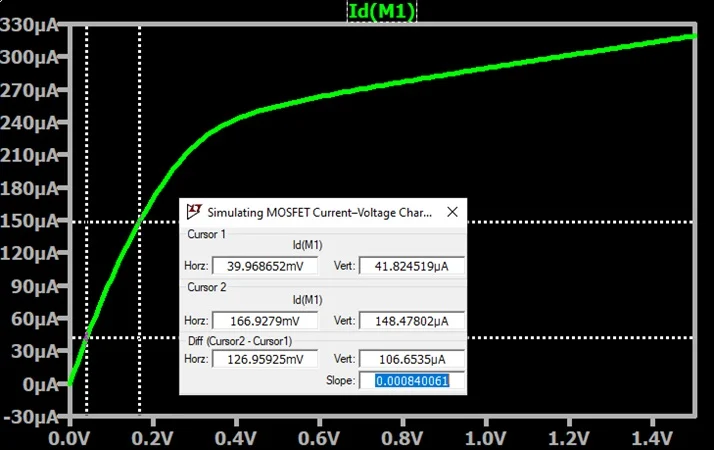

这只增加了一个步骤。我们使用 LTspice 找到斜率(图 3),然后取逆。

光标框显示漏极电流与漏极电压曲线的斜率。

图 3.在 FET 的线性区域中查找漏极电流与漏极电压曲线的斜率。

该线的斜率为 0.00084。因此,总电阻为 1/0.00084 = 1190 Ω。该总电阻包括 100 Ω 漏极电阻,使得 NMOS 的通道电阻等于 1090 Ω。

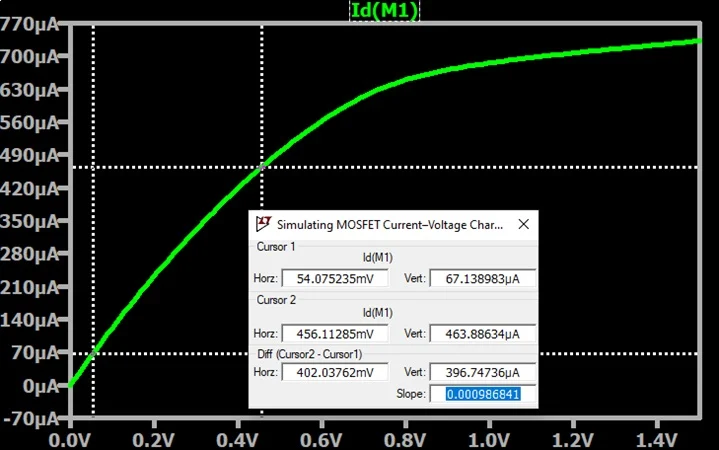

更高的栅极-源极电压使通道更具导电性,因此如果我们增加栅极电压,我们可以预期该电阻会降低。图 4 显示了如果我将栅极电压增加到 2 V 会发生什么情况。

栅极电压增加后,漏极电流与漏极电压曲线的斜率。

图 4.栅极电压增加到 2V 后漏极电流与漏极电压曲线的斜率。

当V GS = 2 V 时,斜率等于 0.00099。取该值的倒数可得出 1010 Ω。减去 100 Ω 漏极电阻后,FET 在线性区域的通道电阻为 910 Ω。这比我们之前的电阻值减少了 180 Ω,因此我们可以认为我们的预期得到了证实。

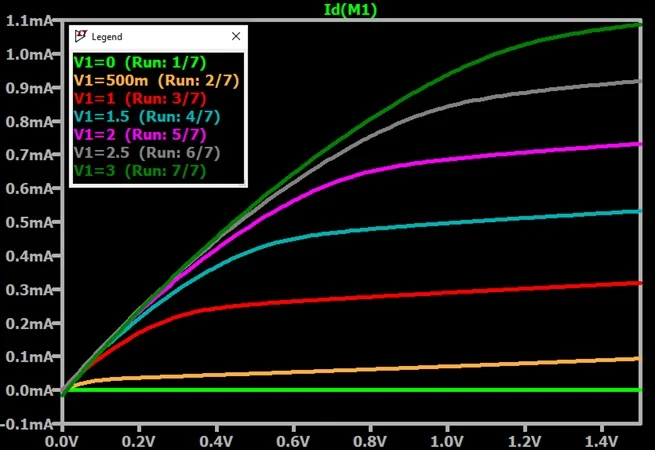

生成一组特性曲线

FET 行为的讨论通常伴随着漏极电流与漏极电压图,该图包含多条曲线来表示不同栅极-源极电压的结果。这使得单个图能够传达有关栅极-源极电压、漏极-源极电压和漏极电流之间电气关系的大量信息。

要在 LTspice 中生成这种类型的图,我们只需修改模拟命令,使其指定 V2 和 V1(即栅极电压)的扫描。新的模拟命令是:

.直流V2 0 1.5 0.01V1 0 3 0.5

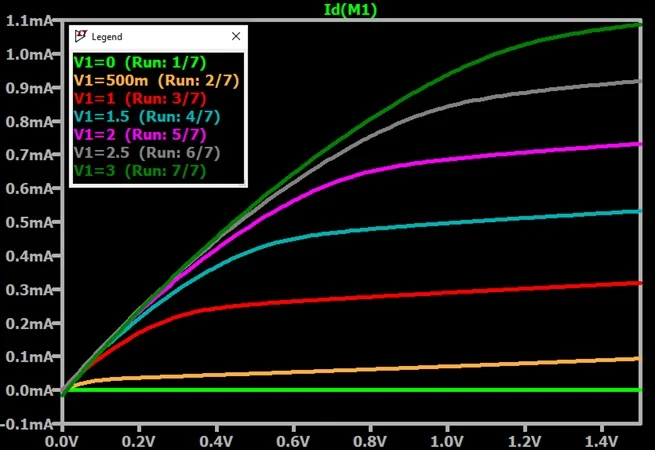

V2 扫描与之前相同,但我们添加了文本,指示 LTspice 将 V1 源从 0 V 以 0.5 V 的增量增加到 3 V。结果就是图 5 中的彩色图。

七种不同栅极电压值下的漏极电流与漏极电压的关系。

图 5.七种不同栅极电压值下的漏极电流与漏极电压的关系。

要使您的图表显示如图 5 所示的图例,请按照以下步骤操作:

右键单击绘图窗口。

前往查看。

选择步骤图例。