在电子测量系统中,常常需要对高速信号进行采集与处理,且在很多领域对数据采集与处理系统的要求还非常高。因此,设计一个好的高速高采集系统尤为重要。对于高速数据采集系统,人们通常选择用FPGA、DSP等高速器件来实现的方法和MCU比起来,其成本较高。其实,在有些系统中,并不要求对数据进行实时采集,这时,用价格低廉的MCU即可实现。本文给出了一个由MCU控制、利用FIFO作为缓冲器的高速AD采样电路,巧妙的实现了高速AD采样与较慢速的MCU数据处理间的链接。

1 系统基本原理

对于高速数据的采集,若将AD采样数据同步读出,对于MCU来说,其速度远远不够。因此,本系统利用高速FIFO作为缓冲器,由FIFO先将高速AD采样数据存储起来,再由MCU将数据从FIFO中低速读出。然后经过前端调理电路将输入的单端模拟信号转换成适合AD输入范围的差分信号。

本系统的MCU采用EZ-USB芯片AN2131Q来实现。AN2131Q是Cypress公司的EZ-USB系列USB总线控制器,有8K字节的程序RAM,外部存储容量可达64KB,有24个通用I/O口。AN2123Q芯片可把USB总线接口所需的信息打包,然后将USB总线收发器与USB总线的引脚D+和D-相连,再用串行接口引擎来对串行数据进行解码和译码、错误校验、位填充并完成USB总线所需的其它信号,终实现总线接口的数据传输。AN213lQ内嵌的增强型8051内核可使用标准的8051指令进行设置,速度较标准型8051更快。

AN2131Q可通过USB口并采用块传输方式将从FIFO中读出的数据传给PC机。本系统主要由AD采样模块、数据缓冲模块和MCU控制模块组成。系统的基本原理框图如图1所示。

|

|

2 主要硬件器件

2.1 AD9238的主要特性和功能

AD9238是ADI公司推出的12位双通道数模转换器芯片。该芯片采用3.3 v供电,速度可选20MS/s、40 MS/s和65 MS/s。它可以提供与单通道A/D转换器同样优异的动态性能,但是比使用2个单通道A/D转换器具有更好的抗串扰性能。AD9238的2个ADC通道除了共用内部的电压参考源VREF外,其它基本都是独立的。AD9238采用流水线工作方式,在每个时钟信号的上升沿进行采样,经过7个时钟周期后,数据出现在数据线上。AD9238的输出数据为TTL/CMOS兼容电平。

AD9238的主要引脚功能如下:

VIN+、VIN-:模拟差分信号输入端。

REFT、REFB:外部基准电压的输入端。

Q0~Q11:12个数据输出位。

OEA、OEB:分别为两通道数据输出使能位。该引脚为低电平时,使能数据总线;该引脚为高电平时,输出为高阻。

PDWNA、PDWNB:分别为两通道的通道关闭功能使能位。该管脚为低电平时,使能通道;该管脚为高电平时,关闭通道。

DFS:输出数据格式选择位。该脚为低电平时,数据输出格式为偏移二进制;该管脚为高电平时,数据输出格式为二进制补码。

OTR_A、OTR_B:分别为两通道的溢出标志位。有溢出时,该管脚输出高电平。

MUX_SELECT:数据复用模式选择位。该管脚为高电平时,两通道数据分别从各自通道输出;该管脚为低电平时,A通道数据从通道B输出,B通道数据从通道A输出;该管脚接时钟时,两通道数据将复用输出数据端口,此时采样速率比前两种提高一倍。

SENSE:基准模式选择位。该管脚接地时,VREF设置成1 V。该管脚直接与VREF管脚连接时,VREF被设置成0.5 V。在该管脚、VREF管脚和模拟地三者之间串接2个电阻R1和R2时,VREF=0.15(1+R1/R2)。上述两种情况都属于内部电压参考。该管脚接到AVDD时,采用外部电压参考。

信号输入分为单端输入和差分输入两种情况。单端输入时,VIN-引脚直接与VREF引脚相连,输入信号与VIN+引脚相连,此时模拟输入电压的范围为;差分输入时,差分信号的两端分别与VIN+和VIN-引脚相连,此时模拟输入电压的范围为2VREF~VPP。

2.2 前端调理电路

为了减少A/D转换结果的二次谐波,提高信噪比(SNR),几乎所有的高速A/D芯片都要求模拟信号为差分输入,因此需要用前端调理电路来将单端信号转换成差分信号。本系统调理电路采用的是ADI公司的AD8138,该放大器具有较宽的模拟带宽(320 MHz,-3 dB,增益为1),可用于驱动12位ADC,非常适用于要求低成本和低功耗的系统。AD8138采用ADI公司的新一代XFCB双极型制造工艺。内部的共模反馈结构使之可以通过施加于一个引脚上的电压来控制其输出共模电压。AD8138内部的反馈环可实现平衡输出,同时可以抑制偶次谐波失真。它的输入阻抗高达6MΩ,可以直接与输入信号相连从而省略隔离放大器,因而可大大精简了电路结构。

2.3 FIFO的主要特性

本设计选用的FIFO是TI公司的SN74V245。SN74V245是一种高速大容量先进先出存储器件。其工作频率为133 MHz,容量为4096×18 bit;SN74V245可以设置成标准工作模式或者FWFT工作模式,可提供全满、半满、全空、将满以及将空等五种标志信号。

写FIFO可由写使能WEN控制,当WEN为低时,可在每个写时钟(WCLK)的上升沿将数据写入。读FIFO则由读使能REN控制,当REN为低时,可在每个读时钟(RCLK)的上升沿将数据读出。读、写相互独立,也可同时进行。FIFO中没有地址指针,可在读、写过程中用相应的状态标志位置位来指示FIFO的状态。为避免数据读空,空标志(EF)置位将禁止读操作;而为了避免数据写入溢出,满标志(FF)置位将禁止写操作。

3 系统的具体实现

运行时,若AD9238的SENSE接地,系统将采用内部基准(VREF=1 V),此时的输入差分模拟信号范围为VPP。如将DFS接高,则AD输出数据的格式为二进制补码。MUX_SESECT接高电平,则可保证A通道数据从通道A输出,B通道数据从通道B输出。AD9238的OEBA、OEBB由MCU控制。

为了使两个通道AD同时工作,提高系统效率。设计时可采用两个FIFO来独立地将两路AD输出数据进行存储。由于AD的数据输出为12位,FIFO存储宽度为18位,故可将FIFO输入端的空脚接地,输出端空脚悬空。

将AD时钟(本设计采用40 MHz)直接与FIFO的WCLK相连,可使FIFO同步将AD采样数据写入,实际上.FIFO的RCLK由MCU控制,FIFO的WEN、REN也由MCU控制。

FIFO的满标志(FF)应接到MCU的外部中断引脚。同时,FF与MCU的控制信号(CONTROL)会通过与非门共同作用于AD的PDWN引脚。MCU通过CONTROL来控制AD的启动。当CONTROL为1时,若FF为1(FIFO不为写满状态)且与非门输出PDWN为0,则启动AD转换;若FF为0且PDWN为0,则关闭AD转换。而如CONTROL为0,无论FF状态如何,PDWN均为0,即不启动AD转换。

AD转换启动后,若FIFO写满,则为0,这样,PDWN也为0,此时硬件将AD通道关闭。同时,MCU进人中断服务程序并读FIFO,然后通过USB总线将读得的数据传给PC机。

将FIFO12位输出数据的高4位和低8位分别接到锁存芯片74HC574,并将74HC574的输出端接到AN2131Q的数据总线上,AN2131Q便可通过片选信号选通要读的FIFO和74HC574,然后分两字节将12位数据读入。

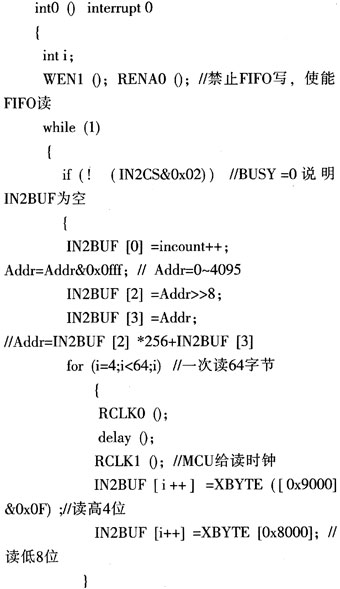

AN2131Q的数据总线和地址总线是独立的,访问外部数据存储器可直接通过一条MOVX指令来实现。USB传输采用块传输,传输的字节数为64。进入中断程序的源代码如下:

|

|

4 系统PCB设计注意事项

4.1 电源和地线的处理

为了降低并抑制整个系统的噪声,其系统电源和地的处理尤为重要。采用的方法是在电源、地线之间加去耦电容。设计时应在每个电源引脚都就近接上去耦电容,并尽量加宽电源、地线宽度,是地线比电源线宽。数字电路部分可用大面积铜层做地线,并在板上把没有用上的地方都与地相连接,以作为地线使用。

4.2 模拟电路和数字电路的共地处理

本系统是由数字电路和模拟电路混合构成的,因此,在PCB设计时要考虑他们之间的互相干扰问题。对信号线来说,高频信号线要尽可能远离敏感的模拟电路器件,而且走线要尽可能短而等长。对地线来说,板内数字地和模拟地是分开的,应采用单点接地的方式,并通过一个磁珠将两者连接起来。事实上,整个PCB对外界应只有一个结点。

4.3 过孔的处理

高速数字电路中,过孔的寄生电感往往会给电路带来较大的负面影响。因此,在PCB设计中尽量做到以下几点:

(1) PCB板上的信号走线尽量不换层,也就是说,尽量不要使用不必要的过孔。

(2) 电源和地要就近打过孔,过孔和管脚之间的引线越短越好,因为它们会导致电感的增加。

(3) 在信号换层的过孔附近放置一些接地的过孔,以便为信号提供近的回路。

5 系统性能分析

高速数据采集系统的动态性能指标主要包括INL、DNL、SNR、SINAD和有效位数(ENOB)等。在本系统的测试过程中,AD采样时钟为40MHz且输入信号为20 kHz的正弦信号时,其实际测试功率谱的密度如图2所示。

图2中,主频率集中在20 kHz处,同时还有一些噪声频率,能量值为73.95。利用Matlab软件可以计算出SINAD为63.2 dB。根据ENOB=(SINAD-1.76)/6.02,可得出:ENOB为10.5。当输入为0 V时,理论上的AD输出值应为7FF,而实际测得的输出数据的平均值为7FB,由此可求出其偏移误差为04H;同样,输人为1 V时,测得系统的增益误差为03H。AD转换位数为12位。而被设置为1 V,则转换为1 V/212=0.024 mV。

6 结束语

经测试分析,本系统能对单一频率的模拟信号准确地进行数据采集和恢复。由于本系统AD的采样速率是40 MHz,FIFO深度为4 KB,故对速率在7.5 kHz~20 MHz的信号,写满FIFO足已使采样点多于一个周期,又不至出现混叠,这样就可以准确地恢复出信号。当然,为了满足各个频率范围内模拟信号的采样,也可以考虑扩大FIFO深度、改变AD采样时钟频率。总之,本文提出的这种由MCU、FIFO实现的采集系统方案比较简单,且实用可靠。

[1]. EZ-USB datasheet https://www.dzsc.com/datasheet/EZ-USB_305660.html.

[2]. TTL datasheet https://www.dzsc.com/datasheet/TTL_1174409.html.

[3]. DFS datasheet https://www.dzsc.com/datasheet/DFS_1872008.html.

[4]. AD8138 datasheet https://www.dzsc.com/datasheet/AD8138_1055531.html.

[5]. SN74V245 datasheet https://www.dzsc.com/datasheet/SN74V245_68324.html.

[6]. 74HC574 datasheet https://www.dzsc.com/datasheet/74HC574_1811820.html.

[7]. PCB datasheet https://www.dzsc.com/datasheet/PCB_1201640.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。