有两种不同的表示方法通常用于分析电路的运行:时域和频域表示。时域分析基于检查电压或电流随时间的变化。

另一方面,频域分析将信号表示为几个具有不同频率的正弦波的总和,并检查响应每个频率分量的电路行为。

如果我们选择合适的表示来分析电路,回答特定问题可能会变得更容易。例如,使用时域表示可以让我们更容易理解用快速逻辑门驱动相对较长的

导线时发生的波反射现象。

但是,例如,如果我们使用频域表示,则可以更好地分析 PC 板的 EMC 性能。由于在某个域中回答给定问题可能更容易,因此我们有时需要能够将时域参数转换为频域参数,反之亦然。

在本文中,我们将研究数字信号的上升/下降时间与其带宽(频域参数)之间的关系。但在此之前,让我们先了解一些重要概念。

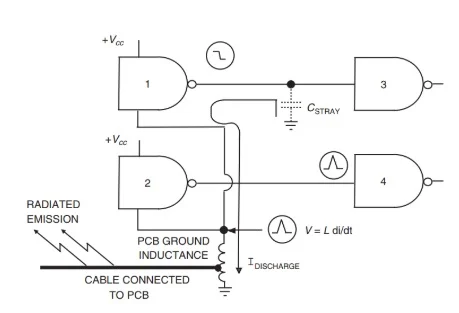

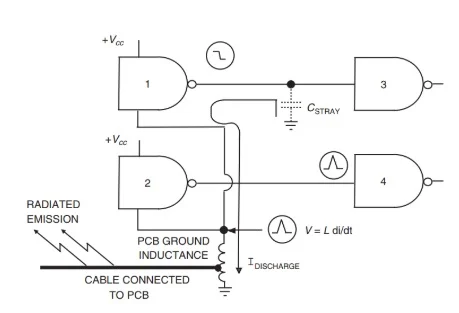

上升时间:一个重要的时域参数 数字信号的上升时间是一个非常重要的时域参数。例如,上升时间可以直接影响 PCB 的接地反弹。如下图 1 所示。

图 1.图片由电磁兼容工程提供。

在该图中,接地路径的

电感由集总

电感器建模。当门 1 的输出从逻辑高变为逻辑低时,存储在 \[C_{STRAY}\] 中的电荷通过接地路径放电。这会导致接地反弹,其公式为 \[V = \frac {\Delta I}{\Delta t}\],其中 \[\Delta I \] 是流过接地电感的放电电流,\[\Delta t \] 是放电时间间隔,与门输出的上升/下降时间有关。

地弹可能导致门 2 的输出端出现噪声电压,如果地弹足够大,甚至会导致门 4 的输出端出现不必要的转换。这只是一个例子,说明了上升时间在高速数字设计中的重要性。我们在上一篇文章中讨论过,当用快速逻辑门驱动相对较长的导线时,足够小的上升时间会导致波反射现象。

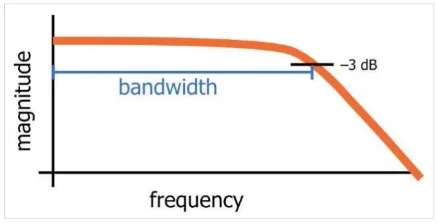

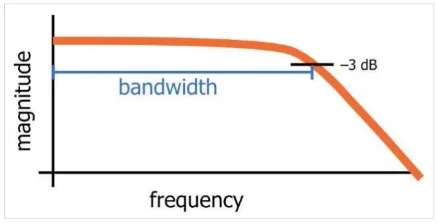

数字信号的带宽 带宽是用于描述电路行为的常见频域参数。例如,我们通常考虑使用 3 dB 带宽来描述

滤波器或通信信道的频率响应。如图 2 所示,低通滤波器的 3dB 带宽是频率响应的一部分,位于 DC 时传递函数幅度的 3 dB 以内(在此图中,DC 时的幅度为 0 dB,在传递函数带宽的远端下降到 -3 dB)。

图 2. Robert Keim 通过AAC创建的图像

虽然上述带宽定义描述了电路的行为,但带宽还有另一种定义,它描述了数字信号的频率内容。此定义指定了数字信号频谱内容中显著频率分量。

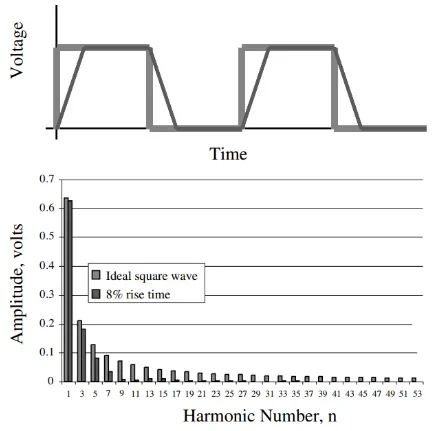

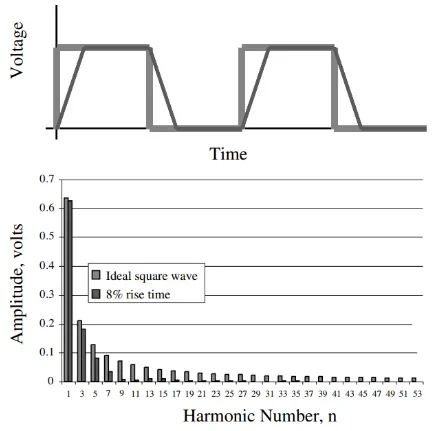

稍后我们将解释此定义中使用的“显著”一词,但在此之前,理想方波的带宽是多少?50% 占空比理想方波(上升/下降时间为零)的频谱内容包括其基频的所有奇次谐波。对于此理想方波,带宽是无限的。 然而,在现实世界中我们无法获得这种理想信号,因为产生该信号的设备或用于传输该信号的互连将不可避免地表现出有限的带宽。因此,我们设备/互连的 3-dB 频率以上的所有谐波都将被衰减。由于这些高频谐波被抑制,我们将不再有零上升时间方波。相反,我们将得到一个梯形波形,需要一些时间从低到高或反之亦然。下图 3 将梯形信号与理想方波进行了比较。

图 3. 图片由Signal and Power Integrity-Simplified提供。

上图还显示了两个信号的频率内容。如您所见,梯形波形频谱中的高频谐波明显衰减(与理想方波相比)。由于梯形波形没有高频分量,因此它无法实现急剧转变所需的快速变化。

如上所述,理想方波具有无限带宽,但上述梯形波形的带宽是多少? PCB 设计师 Eric Bogatin 所著的《信号和

电源完整性 - 简化》一书指出,如果梯形波形(具有任意上升/下降时间)的频率分量的幅度与理想方波的相同谐波相比衰减大于 0.7 倍,则该频率分量被充分衰减,并且不是信号频谱中的重要频率分量。仅考虑重要频率分量,我们就可以找到给定梯形波形的带宽。

例如,通过目视检查图 3,我们观察到第 7 次谐波衰减了大于 0.7 倍(与理想方波的相同谐波相比)。因此,该谐波并不重要。但是,根据上述定义,第 5 次谐波似乎很重要。因此,该梯形波形的带宽从 DC 延伸到第 5 次谐波。如果波形周期为 10 ns,则基波谐波将为 100 MHz,带宽将为 500 MHz。

上升时间和带宽

我们看到,在实践中,我们不能有零上升时间。梯形波形的非零上升/下降时间对应于频域中的有限带宽。有一个近似值将信号的上升时间与其带宽联系起来:

\[BW = \frac {0.35}{T_r}\]

在这个等式中,\[T_r\] 是信号的 10-90% 上升时间。10-90% 上升时间是信号从其终值的 10% 变为其终值的 90% 所需的时间间隔。例如,如果信号的上升时间为 0.5 ns,则其带宽将为 700 MHz。

互连如何改变信号上升时间?

在本文的一部分,我们来简单看一下一个有趣的问题。

如果我们将给定上升时间 \[T_{r, in}\] 的信号通过带宽为 BW 的电路,会发生什么情况?电路的有限带宽如何影响信号上升时间?

例如,假设我们将信号通过一条 4 英寸长的传输线,其带宽为 BW。如果 BW 足够低,它可以抑制输入信号的一些频率成分,使它们变得不重要(我们在上面解释了在这种情况下“重要”的含义)。

由于部分高频分量受到抑制,信号到达互连远端时上升时间可能会增加。因此,低带宽电路/互连可以增加信号的上升时间。

下面的公式可以量化这种影响:

\[T_{r,输出} = \sqrt{T^2 _{r,输入} + T^2 _{r,系统}}\]

这里,\[T_{r, out}\] 是互连输出的上升时间,\[T_{r, system}\] 是与互连相关的上升时间。可以使用上一节讨论的公式从其带宽获得互连上升时间。例如,如果互连的带宽为 6 GHz,我们可以将 58.3 ps(皮秒)的上升时间与此互连相关联。现在,如果我们向此互连发送一个 \[T_{r, in} = 50 ps \] 的信号,则在互连的远端,信号的上升时间将增加到 76.8 ps。