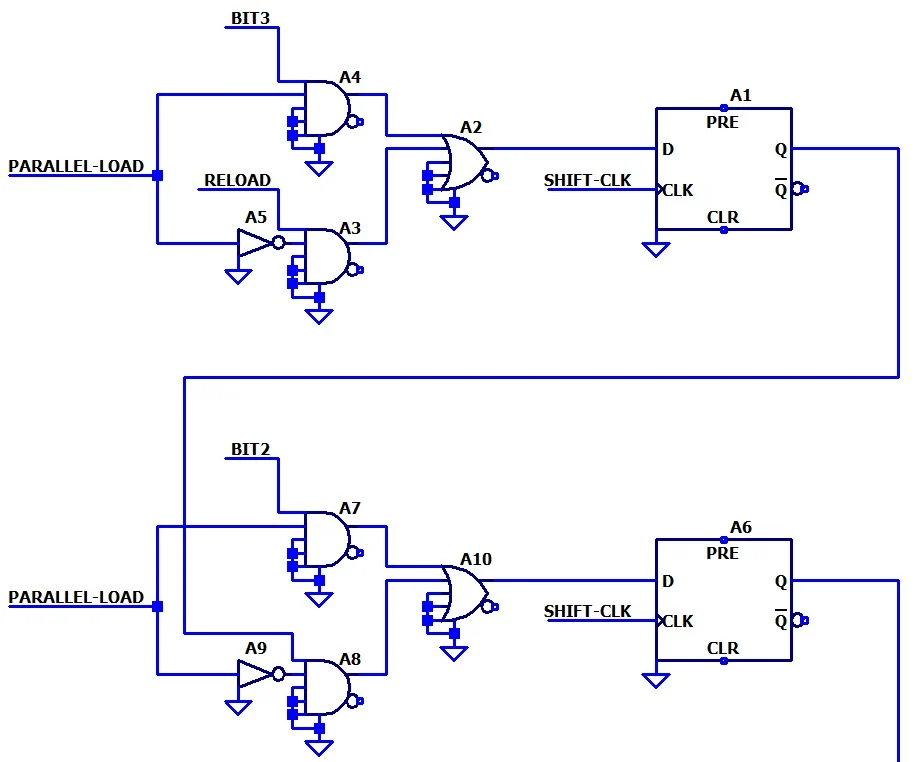

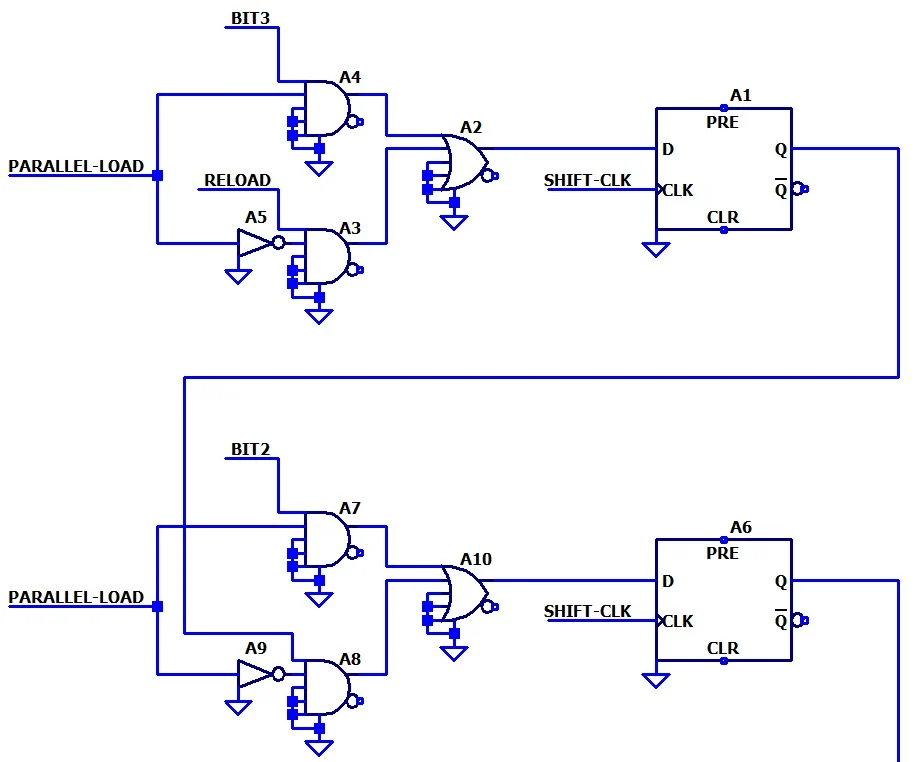

图 1 传达了寄存器内存单元的结构和互连。

LTspice 并行负载移位寄存器中的前两个

触发器及其相关的逻辑门。 图 1. LTspice 并行负载移位寄存器中的两个触发器及其相关的逻辑门。

在本文中,我们将观察该寄存器的操作并探讨它的一些设计细节。

使用

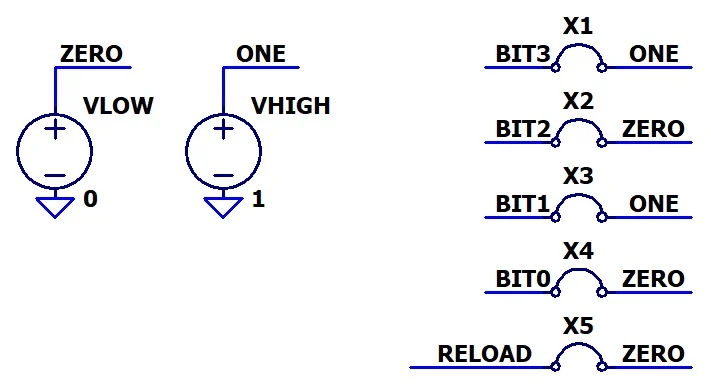

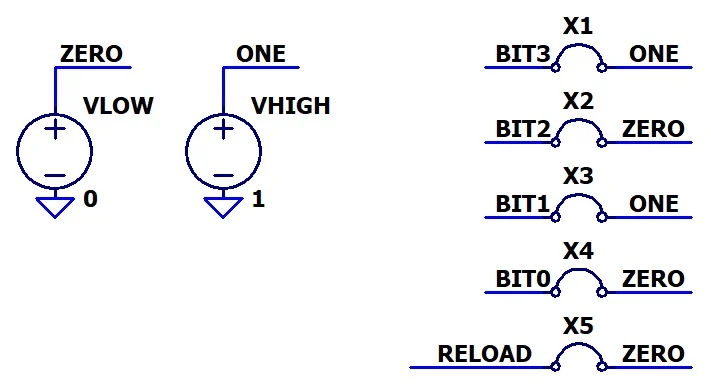

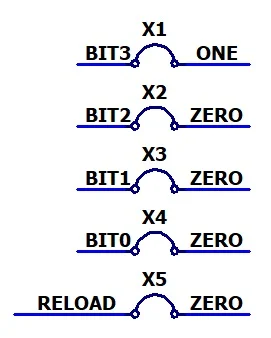

跳线创建数字数据 您可能还记得上一篇文章,该寄存器是一个四位设备。原理图中的每个四位都有一个名为BITn的输入信号,其中n是 0 到 3 范围内的整数。图 2 显示了我针对如何方便地为并行加载操作指定预选四位数字字的问题的解决方案。

并行负载值是借助 LTspice 跳线元件分配的。

图 2.借助 LTspice 跳线元件分配并联负载值。

标记为 X1、2、3、4 和 5 的组件是跳线。跳线组件的用途主要是视觉上的,可在 LTspice 的“Misc”库中找到。跳线符号传达的概念与电路板上的物理跳线相同 - 它允许两个名称不同的网络进行电气连接。

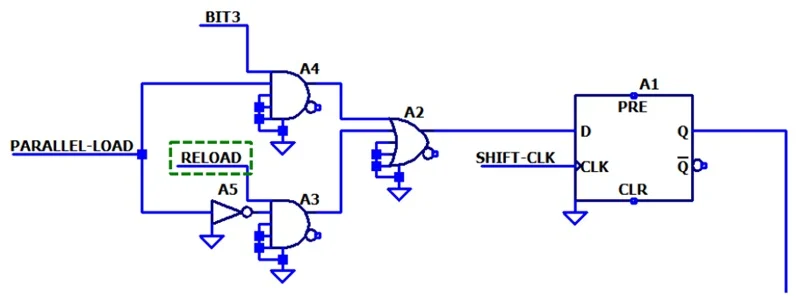

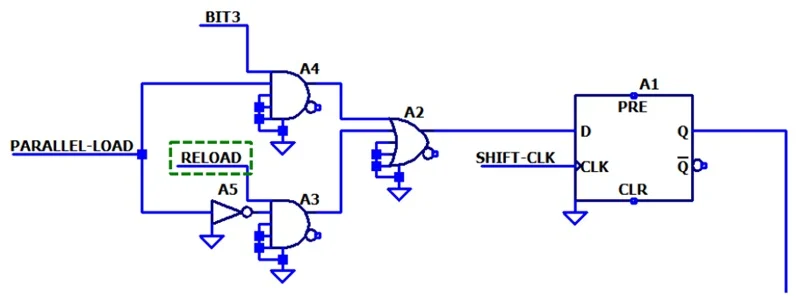

除了四个BIT信号外,还有RELOAD信号。如图 3 所示,RELOAD是移位序列中个触发器的主要输入。这意味着RELOAD在其他位移出寄存器时保留移入寄存器的位。 寄存器中个触发器的主输入标记为 RELOAD。

图 3.当寄存器数据移出时,新数据通过RELOAD信号移入。

回头参考图 2,您会看到我已将RELOAD绑定到ZERO。这意味着一旦寄存器移出所有位,它就会变空(用零填充)。如果您希望寄存器重复移出预选序列,则可以将RELOAD连接到一个触发器的输出。

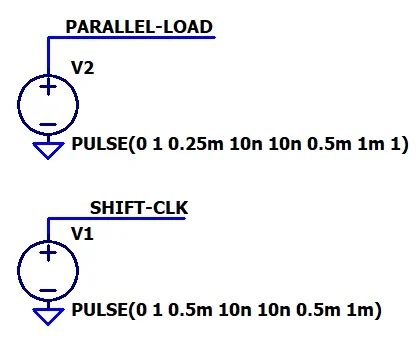

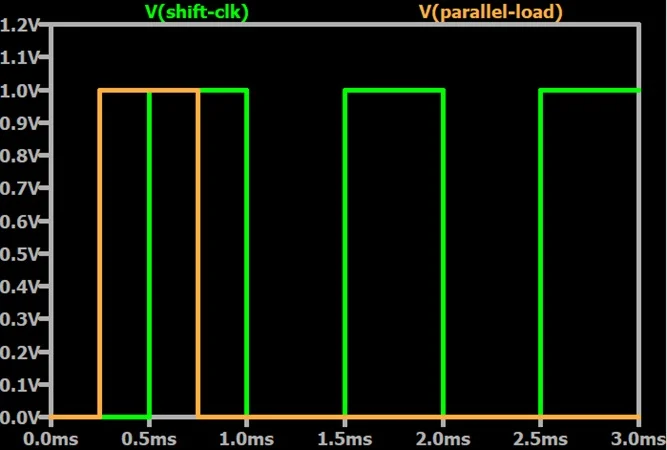

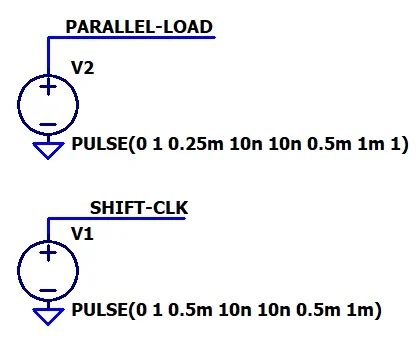

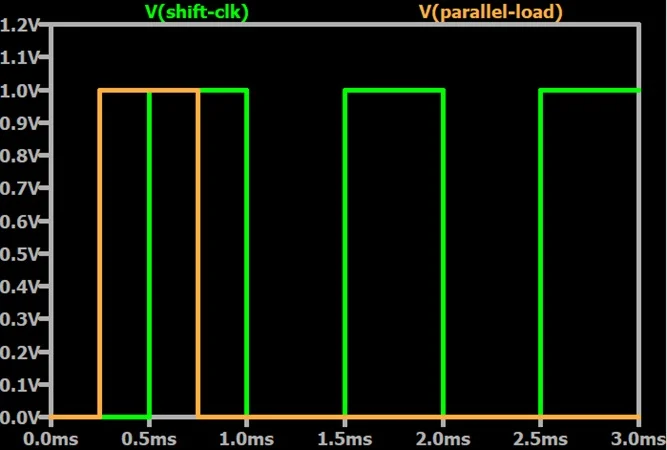

并行负载演示 图 4 显示了寄存器的两个控制信号PARALLEL-LOAD和SHIFT-CLK的生成方式。由于我使用 PULSE 函数指定了 1 毫秒的周期,因此寄存器的移位频率为 1 kHz。

该寄存器的移位频率为 1 kHz。

图 4. 生成寄存器的控制信号。移位频率为 1 kHz。

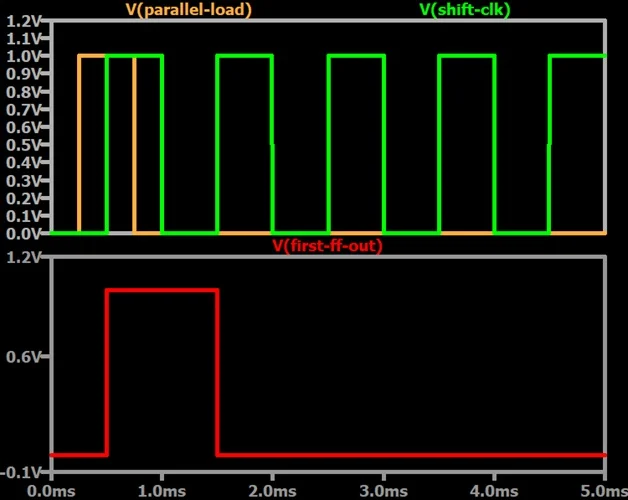

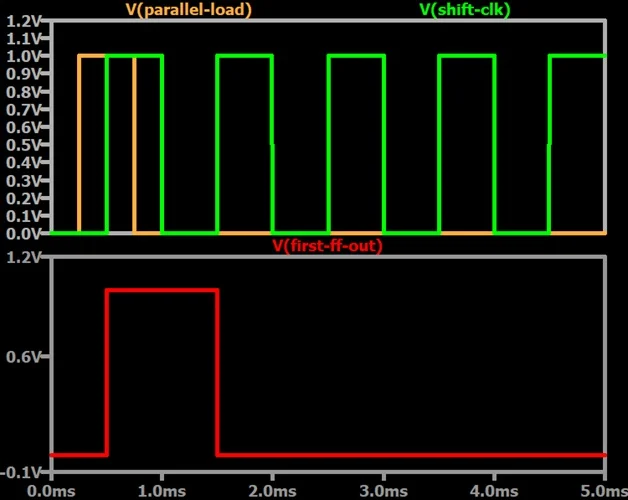

如图 5 所示,PARALLEL-LOAD信号在移位时钟次从低到高的转换过程中处于高电平有效状态。因此,并行数据在系统的个时钟周期内加载到寄存器中。 输出转换显示了移位时钟和高电平有效的 PARALLEL-LOAD 信号之间的关系。

图 5.输出转换显示了移位时钟和高电平有效的PARALLEL-LOAD信号之间的关系。

此后的每个时钟周期,时钟的上升沿都与出现在一个触发器的输出上的新的串行位相一致,这也是移位寄存器的输出。

如果我们检查图 6 中的信号活动,我们可以更轻松地看到移位动作。红色轨迹表示序列中个触发器的输出。 个触发器的输出在加载逻辑高电平后,重新加载逻辑低电平。

图 6.移位序列中个触发器的输出,当它首先并行加载逻辑高电平,然后重新加载逻辑低电平时。

注意F

IRST-FF-OUT的两个转换如何与移位时钟的上升沿一致。由于BIT3与

ONE绑定,因此信号在次转换时变为逻辑高电平。然后,由于RELOAD信号与ZERO绑定,因此它在第二次转换时变为逻辑低电平。

通过寄存器移位数据

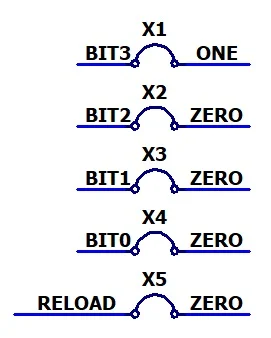

接下来,让我们看看并行加载操作后会发生什么。对于此模拟,我使用图 7 所示的跳线设置。我们的四位字现在不是 0101,而是 0001。 新模拟的跳线设置。BIT1 现在与 ZERO 绑定,而不是 ONE。

图 7.新模拟的跳线设置。

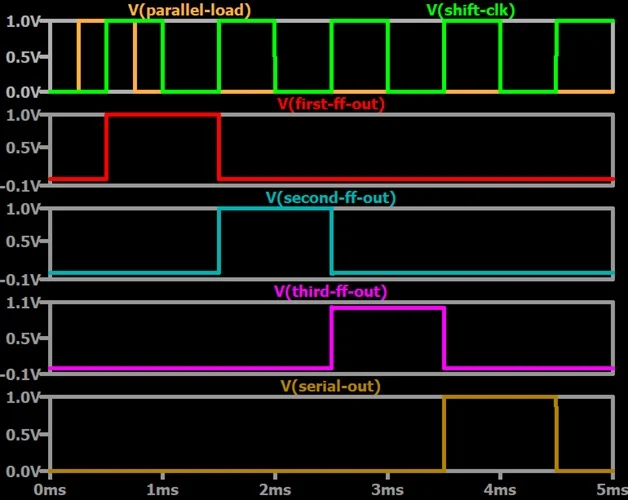

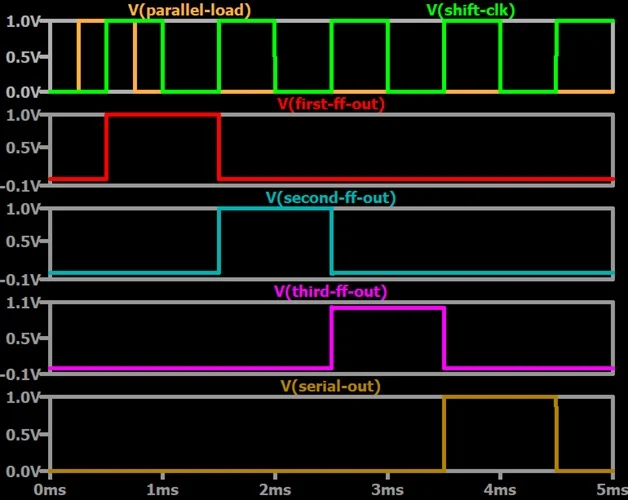

首先,BIT3被加载逻辑高电平值。图 8 显示了该逻辑高电平信号如何通过移位寄存器传播——从BIT3到BIT2再到BIT1,到BIT0。 寄存器的四个触发器的时序图。

图8.寄存器中所有四个触发器的时序图。

您可以通过观察 1 毫秒整数倍的SERIAL-OUT来识别串行比特流。触发器的输出在时钟的上升沿转换;因此,我们希望在输出信号稳定的下降沿进行采样。

例如,上图时序图中的前三个上升沿分别与 0.5 毫秒、1.5 毫秒和 2.5 毫秒对齐。因此,正确的采样时刻为 1 毫秒、2 毫秒和 3 毫秒。这由图 9 中的白色虚线表示。 0001 以串行格式出现在一个触发器的输出上。

图 9.预选的四位字 (0001) 以串行格式出现在一个触发器 ( SERIAL-OUT ) 的输出端。

传播延迟和模拟时间步长

正如我们在本系列文章前面所讨论的那样,在 LTspice 中准确模拟数字电路有时需要我们指定自定义设备参数。在这种情况下,您需要指定传播延迟和时间步长,以确保移位寄存器可靠工作。

LTspice 的默认传播延迟 ( T d ) 为零,这意味着信号从输入瞬间传播到输出。没有任何延迟,一个触发器的输出信号可以如此快速地改变状态,以至于序列中的下一个触发器没有时间响应时钟的上升沿来采样信号。

结果是位不会通过寄存器传播。您可以通过为每个触发器指定合理的T d值来避免此问题。我使用了 1 μs,如图 10 所示。

指定移位寄存器的时间延迟。

图10.移位寄存器的时间延迟规格。

触发器输出信号上的振铃是您可能遇到的另一个奇怪问题。如图 11 所示。

个触发器输出上振铃的示例。

图 11.触发器输出转换后振铃的示例。

图 12 中的特写视图让我们更清楚地看到振荡。

上图中振荡的放大视图。

图 12.图 11 中的杂散振荡的特写。

振铃是由 LTspice 仿真引擎与数字元件生成时间步长信息的方式之间的某种冲突引起的。我设法通过为仿真指定适当的时间步长来消除该问题。如图 13 所示,我选择的时间步长为 50 ns,这比我为触发器选择的 100 ns 上升/下降时间要短(图 10)。

指定模拟时间步长。

图 13.指定模拟时间步长。