LTspice主要用于模拟仿真。然而,通过整合其数字元件目录中的逻辑功能,我们也可以使用它来验证混合信号电路。我们在前两篇文章中研究了LTspice数字元件的结构和仿真行为。在本文中,我们将使用它们来构建并行负载移位寄存器。

寄存器是数字和混合信号IC的关键子电路。在寄存器中,多个单比特存储单元(通常是

触发器)连接在一起,形成一个多位存储设备。例如,我们需要以下内容来制作一个单字节寄存器:

允许我们同时从所有八个触发器读取数据或将数据写入所有八个触发器的连接。

我们刚才描述的是一个基本的并行输入、并行输出寄存器。在移位寄存器中,我们可以将数字数据从一个触发器移动到下一个触发器。此功能允许我们将并行数据转换为串行数据。

例如,假设我们将一个字节的并行数据加载到移位寄存器中。我们可以按顺序通过寄存器的触发器移动其组件位。然后,序列中的一个触发器将原始字节输出为八位序列。

LTspice移位寄存器 对我来说,设计一个只接受串行输入并产生串行输出的移位寄存器相对简单。触发器将连接输出到输入,序列中个触发器的输入

引脚将是整个寄存器的串行输入

端子。并行负载移位寄存器虽然更有用,但也更复杂。它能够将并行数据转换为串行数据,需要组合逻辑来实现多路

复用器功能。

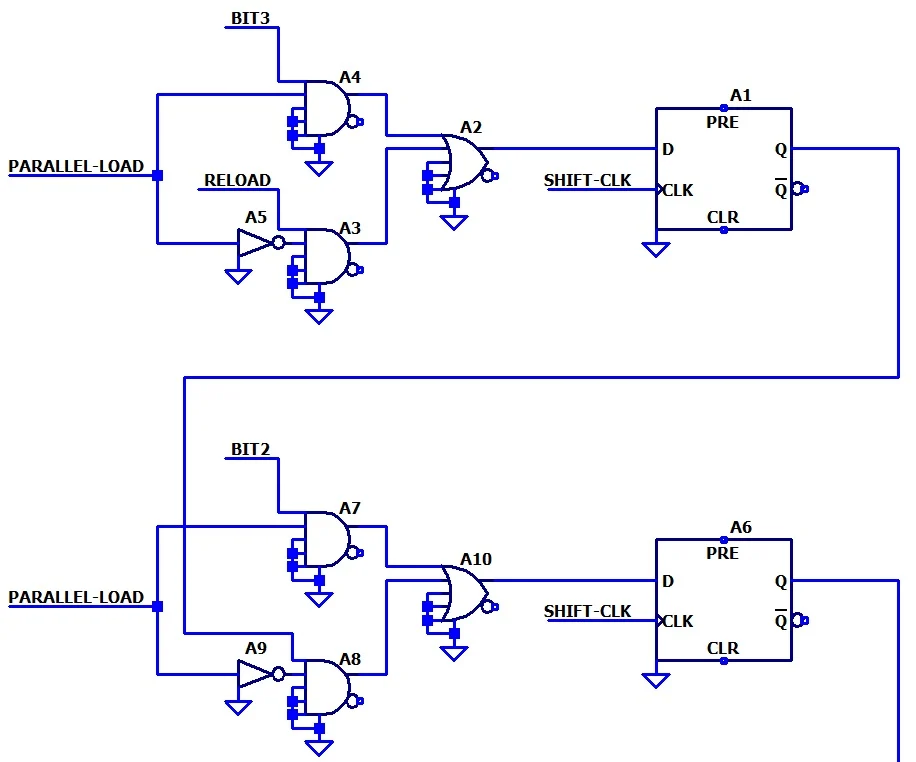

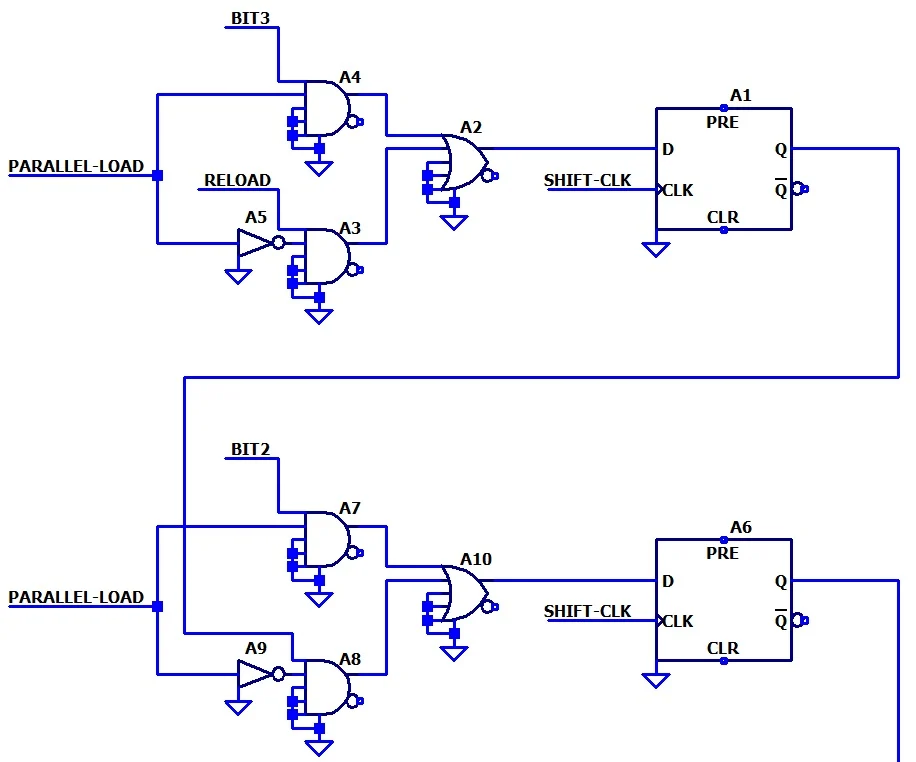

图 1 显示了并联负载移位寄存器中的前两个触发器。每个触发器都相当于一个连接到输入引脚的二对一

多路复用器。

LTspice并行负载移位寄存器中的两个触发器和相关的组合逻辑。

图 1.两个触发器,具有相关的组合逻辑,位于LTspice并行负载移位寄存器中。

从原理图的这一部分,您可以看到:

寄存器每个位的设计。

一个位如何连接到序列中的下一个位。

我将此移位寄存器设计为四位设备,尽管它可以很容易地扩展到八位或更多位。SPICE软件没有针对仿真数字逻辑进行优化,因此在LTspice原理图中可以包含多少数字电路存在实际限制。尽管如此,LTspice可以很好地处理数字元件,并且像本文中讨论的电路不需要很长的仿真时间。

现在我们已经熟悉了移位寄存器的基本结构,我们可以仔细看看它的组合逻辑。

重要提示:本原理图中的所有 AND 和 OR 门都有三个未使用的输入连接到公共端子。LTspice的一个特点是,这样做会从仿真中删除这些输入,从而使门充当双输入逻辑门。对于AND门,这与将这些输入连接到逻辑低电平输入或接地不同。

了解多路复用器电路

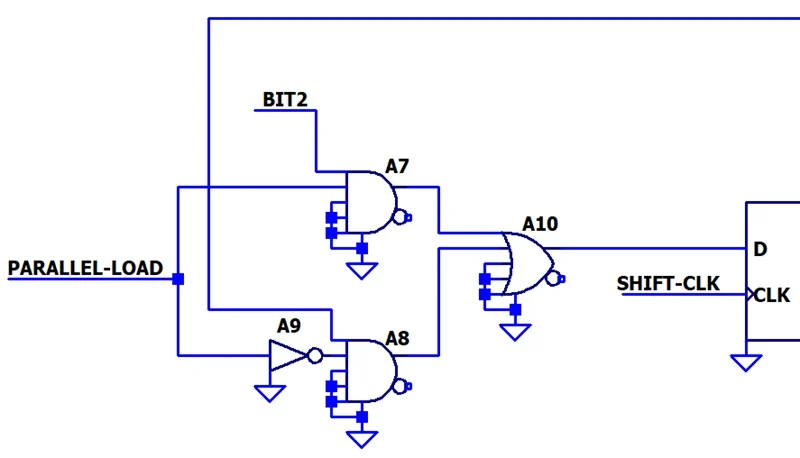

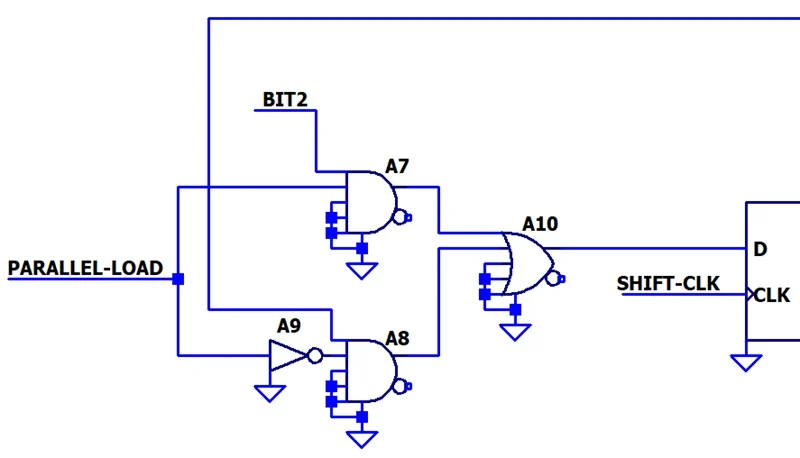

让我们一步一步地了解移位寄存器组合逻辑的功能。我们将使用图 2 中所示的参考指示符进行讨论。其他逻辑模块具有不同的参考指示符,但以相同的方式工作。 LTspice移位寄存器中一个触发器的组合逻辑。

图2.移位寄存器中一个触发器的组合逻辑。

触发器有两个输入信号:

主输入是从前一个触发器的输出端接收到的逻辑电压。它连接到 AND 门 A8。

次级输入是标记为 BIT2 的信号。它连接到 AND 门 A7。

PARALLEL-LOAD信号决定了哪个输入信号将处于活动状态。对于 A7,PARALLEL-LOAD 是其两个输入信号中的第二个;对于 A8,第二个输入信号是 PARALLEL-LOAD 的倒数。这保证了在任何给定时刻,只有一个AND门输出可以为逻辑高电平。

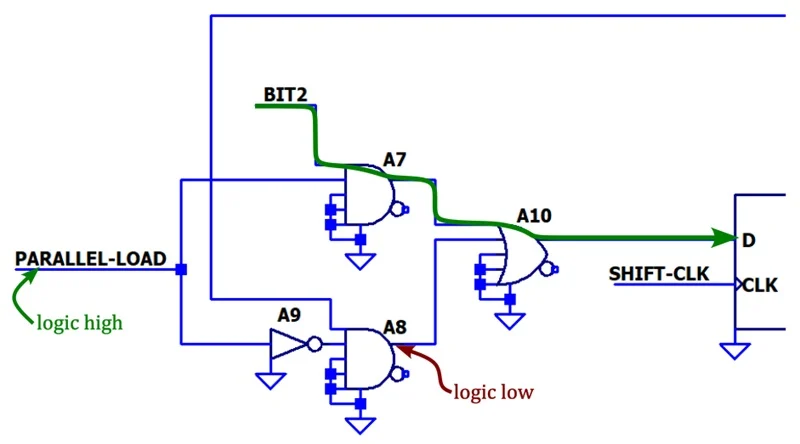

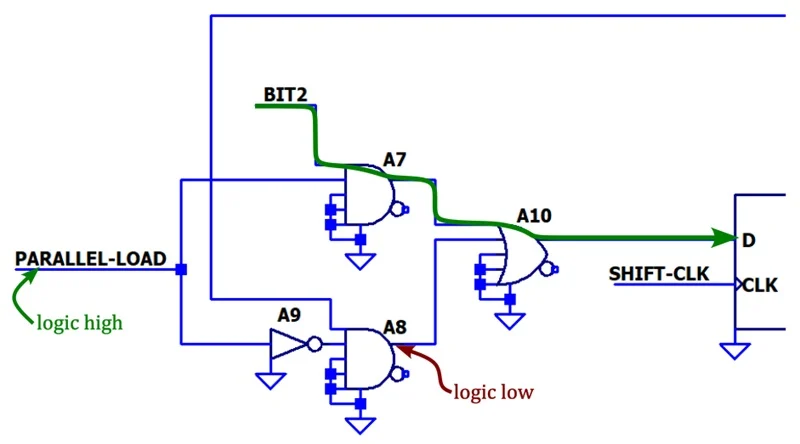

为了将并行数据加载到寄存器中,我将 PARALLEL-LOAD 设置为高电平。AND 门 A8 的输出被驱动至逻辑低电平,A7 通过信号 BIT2。然后,该 BIT2 值通过 A10 传递到 D 触发器的输入端,如图 3 中的绿色长箭头所示。 移位寄存器处于并联负载模式时的信号流。

图3.寄存器处于并联负载模式时的信号流 (PARALLEL-LOAD = 高电平)。

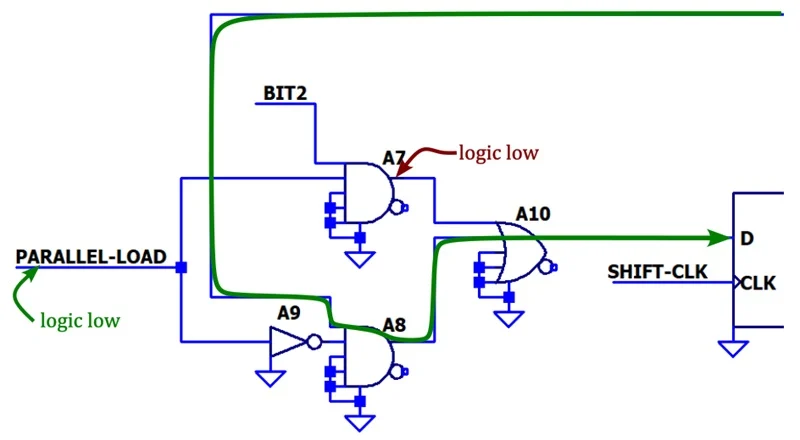

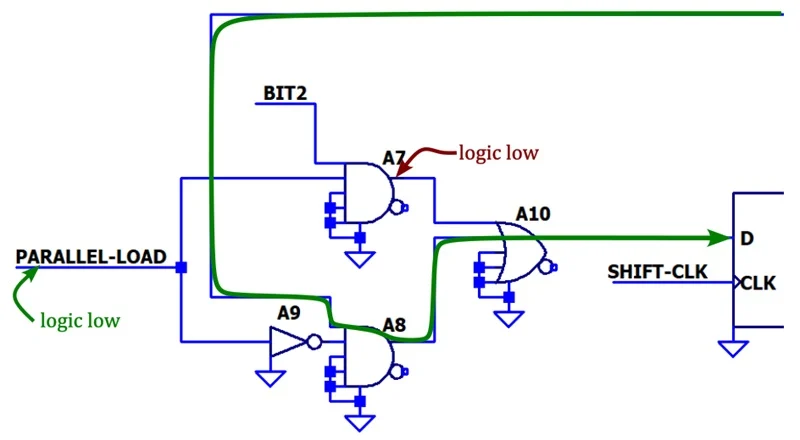

为了在移位模式下操作寄存器,我将PARALLEL-LOAD设置为低电平。这会强制 A7 的输出达到逻辑低电平。因此,BIT2 信号被忽略。

同时,A8的输出再现了前一个触发器输出信号的逻辑电平。信号从 A8 传递到 A10,再从 A10 传递到下一个触发器的输入。触发器的输入现在等于前一个触发器的输出。图4显示了该信号的路径。 寄存器处于移位模式时的信号流。

图4.寄存器处于移位模式时的信号流 (PARALLEL-LOAD = 低电平)。

请注意,图3是一个同步并联负载。当PARALLEL-LOAD为逻辑高电平时,预选位值(BIT2)成为D触发器的主输入,而D触发器的主输入仅响应时钟上的转换而传输到输出。LTspice D触发器是一款上升沿敏感器件。因此,成功的并行负载操作要求在时钟从逻辑低电平转换到逻辑高电平时,PARALLEL-LOAD信号处于活动状态。