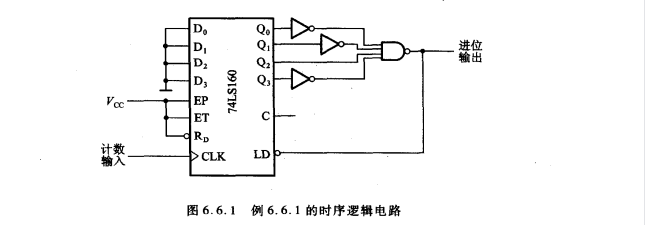

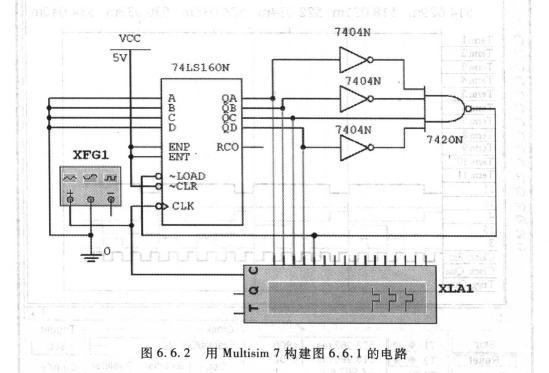

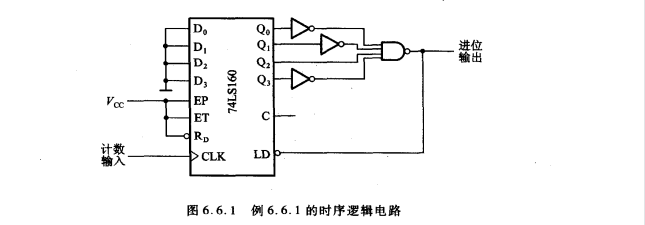

QD进位QD输出QDQD易历史EPVαCETR计数LDCLK输入图6.6.1 例6.6.1 的时序逻辑电路解: 在 Multisim 7 中选用TTL 器件库中的74LS160、反相器7404 以及与非门7420 构成图6.6.1 中的电路,并接入信号发生器XFG1 和逻辑分析仪 XLA1,如图6.6.2所示①。图6.6.2中的QA,QB,Qc,Q0与图6.6.1中的、Q,Q、Q,Q对应。

利用 Multisim 7 中的逻辑分析仪对计数器的时钟波形和输出波形进行观测,得图6.6.3 所示的波形图。分析波形图可见,每5个时钟周期输出波形就重复一遍,在7420的输出端产生一个输出进位脉冲。因此,这是一个五进制计数器。

从逻辑分析仪给出的、Qv,Qc,Q5、Q4的波形图,还可以画出电路的状态转换图,如图6.6.4所示。

图6.6.1 中的计数器采用了同步预置数的工作方式,当计数器处于QvQcDBQA=0100时,用 7404 和 7420 译出LD′=0的信号,将DDDD=0000 的信号预置入计数器,作为计数循环的初始状态。由此分析可得,该计数器是五进制计数器。因此,用Multisim 7 得到的仿真结果与理论分析结果完全吻合。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。