标准 CMOS 多路复用器

在某种程度上,PTL 带来高效的多路复用器并不奇怪。复用与基本布尔函数不同。当我们处理 AND、OR、NOT 等时,我们使用逻辑门来实现逻辑函数。这是有道理的。

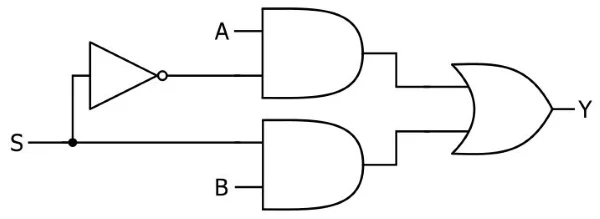

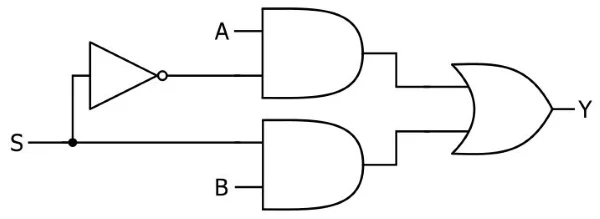

另一方面,多路复用更像是我们可以使用逻辑门实现的切换功能,因为它们很容易获得并且可以完成工作。它们确实完成了工作,但效率不高——下面所示的门配置对于像在两个输入信号之一之间进行选择这样简单的任务来说似乎相当尴尬,特别是当您考虑到每个基于反相器的与门和或门都需要六个晶体管。

标准 2 选 1 CMOS 多路复用器。当S为逻辑低时,Y等于A;当S为逻辑高电平时,Y等于B。

传输门多路复用器

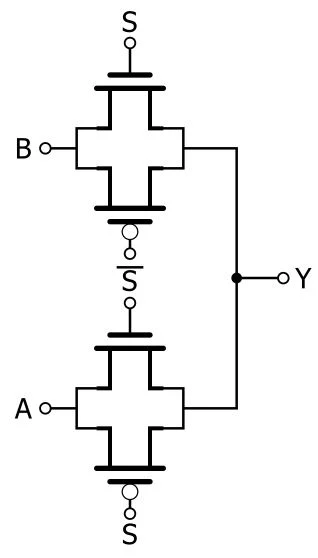

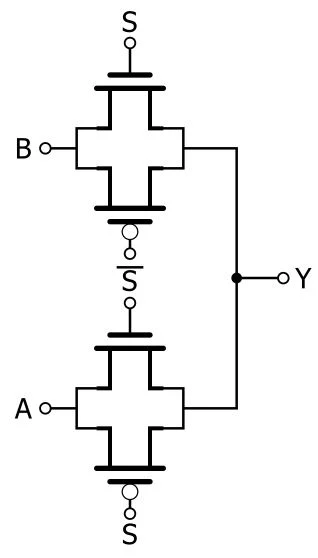

与基于反相器的 CMOS 实现形成鲜明对比,PTL 2 选 1 多路复用器仅需要 6 个晶体管:每个晶体管两个用于两个传输门,两个用于提供 S(选择)信号补码的反相器。

多路复用本质上是电压控制开关,这种类型的功能与传输晶体管操作密切相关,因此上述电路几乎不需要解释。 A输入信号连接至低电平有效传输门,B输入信号连接至高电平有效传输门。当S为低电平时,Y等于A;当S为高时,Y等于B。

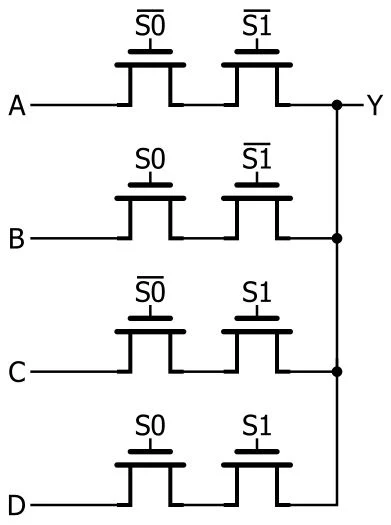

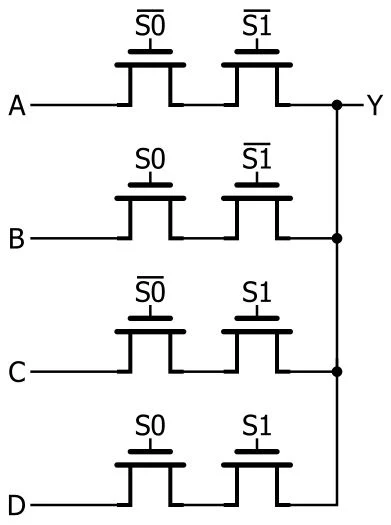

PTL 4 选 1 多路复用器 传输晶体管多路复用器可以使用传输门或“单独 NMOS”类型的开关来构建。就纯逻辑功能而言,它们是可以互换的——它们都根据控制信号的状态传递或阻止输入信号。但是,如果您阅读过之前有关 PTL 的文章,您就会知道传输门可提供卓越的电气性能。

本节讨论的 4 选 1 多路复用器使用 NMOS 开关,主要是因为生成的图更简单。请记住,NMOS 晶体管或多或少是实际电路中使用的任何类型的通过/阻塞元件的占位符。在许多情况下,传输门将是实现,或者如果您想在实验室中试验这些电路,您甚至可以用继电器或MEMS 开关替换 FET 。

由于有四个输入信号,我们需要一个两位选择信号。这两位提供了四种可能的二进制数,每个数字对应于输入信号之一。 S 信号上方反转条的存在(对应于逻辑高)或不存在(对应于逻辑低)可用于将该图转换为功能描述:

如果 S0 = 0 且 S1 = 0,则 Y = A。

如果 S0 = 1 且 S1 = 0,则 Y = B。

如果 S0 = 0 且 S1 = 1,则 Y = C。

如果 S0 = 1 且 S1 = 1,则 Y = D。

请注意,该电路需要为每个 S 信号配备一个反相器。我们通常认为反相器是与使用传输门而不是 NMOS 开关相关的缺点,但在这种情况下,即使 NMOS 实现也需要反相器,因为多路复用器的目的是始终将输入信号之一传递到输出。换句话说,逻辑低选择信号不仅用于阻止而且用于通过,逻辑高选择信号不仅用于通过而且用于阻止。因此,我们需要逆变器。

设计传输晶体管多路复用器

PTL 多路复用器的总体思路是配置串联开关,使得给定的 S 输入组合将输入信号之一传递到输出节点。如果有四个输入,如上所述,则每条输入线上需要两个控制信号和两个串联晶体管。如果有八个输入,则每条输入线需要三个控制信号和三个晶体管。等等。

PMOS 与 NMOS

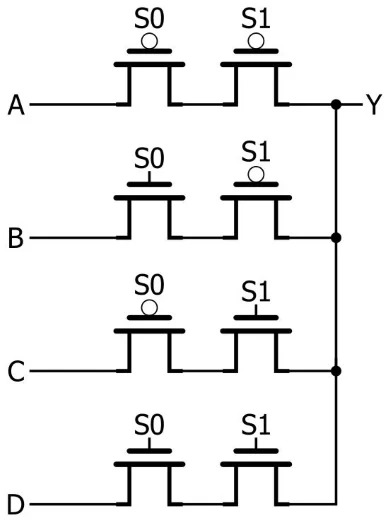

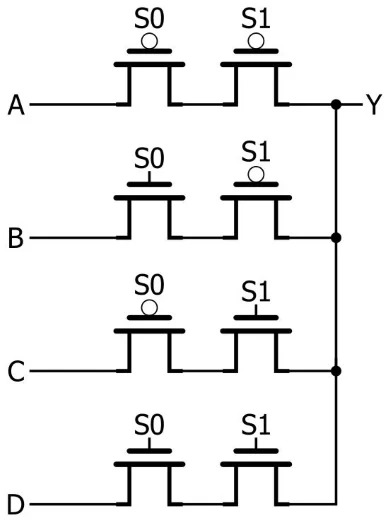

您可能想知道是否可以组合使用 PMOS 开关和 NMOS 开关。 4 选 1 PTL 多路复用器需要在控制电压为逻辑低电平时传递信号的开关。我通过使用选择信号的反相版本来实现这一点,但如果我们使用 PMOS 器件作为“低电平有效”开关,我们就可以消除反相器。 PMOS 加 NMOS 解决方案如下所示:

这将是一个功能电路,但我相信 NMOS 版本在实际应用中将是,尽管 PMOS 器件的使用减少了总体晶体管数量。电子比空穴具有更高的迁移率,因此 NMOS 晶体管(以电子作为多数载流子)的电气性能优于物理等效的 PMOS 晶体管(以空穴作为多数载流子)。

这个问题与多路复用器设计尤其相关,因为使用 PMOS 器件不仅会导致性能较差,而且性能不一致:输入线的输入到输出电气特性会根据每条线的通过/阻止数量而变化元件是PMOS晶体管。