但是,三极管区域不仅受电阻控制,而且受一个相当复杂的方程控制:

I_D=\mu_nC_{ox}\frac{W}{L}\left(\left(V_{GS}-V_{TH}\right)V_{DS}-\frac{1}{2}V_{ DS}^2\右)(这是针对 NMOS 器件;PMOS 器件将具有 μ p而不是 μ n。)但是,如果我们忽略 V DS 2项,则方程可以简化如下:

I D = μ n C o x W L( V G S – V T H ) V D S

现在我们确实在漏源电流 (I D ) 和漏源电压 (V DS ) 之间存在线性(即电阻)关系。然而,“电阻”并不是恒定的,就像单纯的电阻器一样;相反,电阻对应于

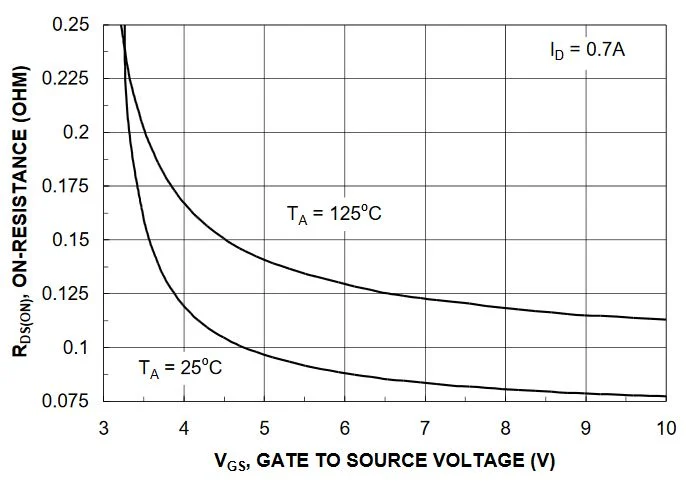

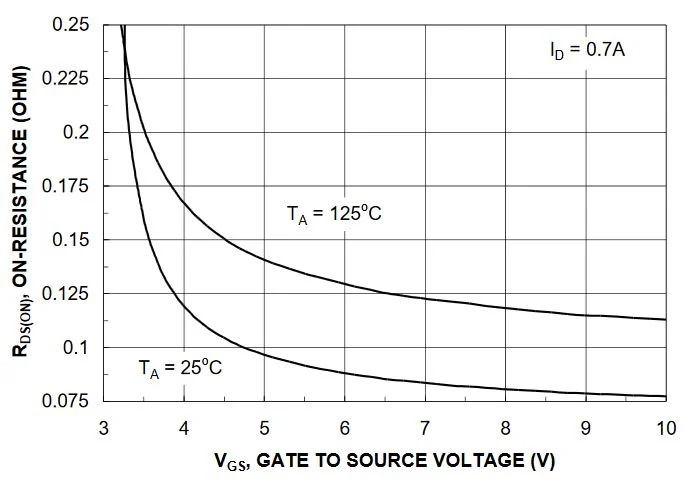

该部件的典型阈值电压为 2.1 V。如果您快速查看 V TH规格和 R DS(on)规格,您可能会认为可以使用 3.3 V 逻辑信号驱动该 FET,并且实现所宣传的导通状态电阻性能。考虑到数据表明确指定了与 R DS(on)规格相对应的栅源电压,这有点粗心;然而,一两个 R DS(on) /V GS数据点并不能体现通态电阻的极端增加,这种情况适用于实际上远高于典型 V TH的栅源电压。因此,这个故事的寓意是 1) 请记住,导通状态(即三极管区域)电阻取决于 V GS,2) 有关详细信息,请参阅 R DS(on)与 V GS的关系图。

此外,导通状态电阻不等于上面给出的三极管区域方程所表示的电阻。后者是 MOSFET 沟道的电阻,而导通电阻包含其他电阻源——键合线、外延层等。电阻特性受制造技术以及 R DS 不同组件各自贡献的影响( on)根据特定设备的预期电压范围而变化。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。