即使在小型数字设计中,时钟信号也可能被分发到整个系统中的数百个时钟元件。这些高扇出时钟信号负责同步系统的不同子系统或组件。这就是为什么我们需要仔细注意时钟网络的不同路径引入的延迟。

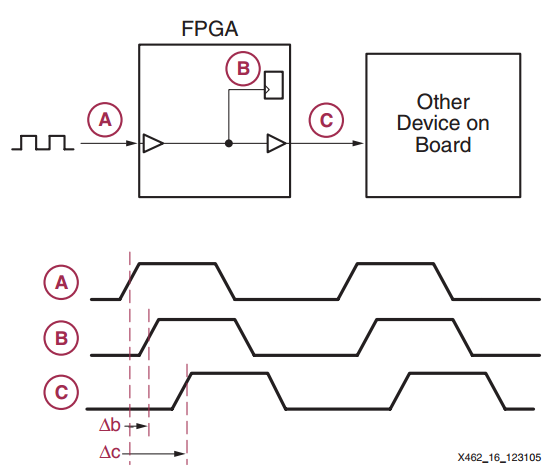

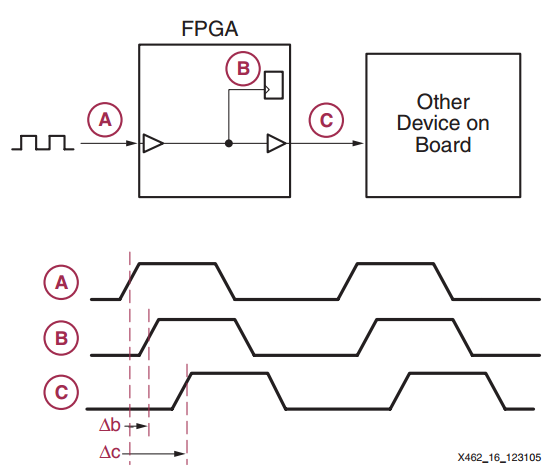

例如,考虑将时钟信号从节点 A 分配到节点 B 和 C,如下图 1 所示。在该图中,时钟信号进入FPGA并经过

缓冲器(如图中的三角形所示),然后到达节点B处的寄存器。该路径具有固有延迟,由$$\Delta b$$表示在波形中。为了将时钟从 A 分配到 C,我们可以使用 PCB 走线而不通过 FPGA,但在图中,FPGA 中分配的时钟用于“板上的其他设备”。该路径的延迟由$$\Delta c$$ 表示。由于$$\Delta b$$和$$\Delta c$$一般不相等,节点B处的寄存器和节点C处的设备将看到略有不同的时钟;应该具有对齐边缘的相同时钟之间的这种固定时间偏移称为时钟偏差。我们可以看到,系统中的高扇出时钟信号具有尽可能小的时钟偏差。

图 1. 分配时钟信号的延迟。图片由Xilinx提供。

生成新的时钟信号

FPGA 的一个理想特性是能够根据系统的要求修改给定的时钟信号以生成新的时钟。例如,假设您设计了一块带有 FPGA 的板。假设 50 MHz 时钟对于电路板来说已经足够,但在 FPGA 中,您需要 200 MHz 时钟来执行特定算法。如果您能够以某种方式从板上的 50 MHz 时钟生成 200 MHz 时钟,则可以避免在系统中使用两个不同的时钟源,并且您也不必以高于必要频率的频率操作板。如果我们回想起某些数字信号处理 (DSP) 应用是多速率的并且在算法的不同部分需要不同的时钟频率,我们就可以确定时钟合成的另一种应用。

现在,让我们看看 FPGA 的时钟相关资源,这些资源使我们能够生成新的时钟信号并将其分发到整个系统。

FPGA的时钟管理资源

当今的 FPGA 包含强大的时钟管理模块,以简化设计过程并降低成本。我们将这些嵌入式时钟管理块称为 CMB。不同的供应商使用不同的术语来指代其 CMB。例如,Xilinx 使用时钟管理块 (CMT) 或数字时钟管理器 (DCM),Intel 使用众所周知的术语锁相环 (PLL),而 Microsemi 使用时钟调节电路。

CMB可以通过执行时钟乘法和除法来生成新的时钟信号。他们也许能够将可编程相移应用于生成的时钟,甚至调整时钟的占空比。CMB 不仅可以对 FPGA 内分布的时钟信号进行去偏斜处理,还可以对从 FPGA 分配到电路板上其他设备的时钟信号进行去偏斜处理(例如进入图 1 中的节点 C 的时钟)。

可编程相移功能的一项应用是将时钟信号与输入数据同步。当我们处理数字信号时,我们必须在数据稳定时(数据转换之后和下转换之前)对信号进行采样。这就是为什么一些 FPGA 提供动态机制来对生成的时钟进行精细相移调整。例如,Xilinx Virtex II Pro 的 CMB 可以应用时钟周期 1/256 的相移。如果没有这种相移能力,时钟可能不会落在数据眼的中心。

具有占空比调整功能的 CMB 对于需要 50% 占空比的时钟信号的应用很有帮助。例如LVDS 和双数据速率 (DDR)

接口等高速通信。如果时钟占空比不是 50%,我们可以使用 CMB 的占空比校正功能来重塑时钟信号,使其具有 50% 的占空比。

为了获得这些功能,FPGA 使用基于锁相环(PLL) 或延迟锁定环 (DLL) 的 CMB。除了 PLL 和 DLL 之外,还有另一组非常重要的与时钟相关的 FPGA 资源:用于在 FPGA 中分配时钟信号的专用缓冲器和路由。这些专用缓冲区和路由使我们能够拥有低偏差时钟网络。

在本文的其余部分中,我们将首先回顾使用 PLL/DLL 实现 CMB 的基本概念。然后,我们将了解英特尔 FPGA 使用的低偏斜时钟网络。

基于 DLL 的时钟偏移校正

图 2 显示了用于补偿时钟分配延迟的 DLL 的基本框图。

图 2.显示使用 DLL 补偿时钟偏差的框图。图片由Xilinx提供。

在该图中,CLKIN是我们打算通过“时钟分配网络”分配的输入时钟。顾名思义,“可变延迟线”模块向 CLKIN 引入可调延迟并产生 CLKOUT。延迟量由“控制”逻辑决定。“控制”块监视其输入并改变延迟,以便两个输入 CLKIN 和 CLKFB 的上升沿对齐。通过这种方式,电路补偿了时钟分配网络中的延迟,理论上我们可以消除时钟分配的偏差。

请注意,“可变延迟线”不能对 CLKIN 应用负延迟来补偿“时钟分配网络”的固有延迟。那么,图2的框图如何消除时钟偏差呢?关键是时钟信号CLKIN是周期性的。为了澄清这一点,让我们考虑图 1 中的时钟偏差示例。从 A 到 B 的路径有 $$\Delta b$$ 的延迟,因此,我们需要应用 $$- \Delta b$$ 的延迟(即负延迟)到节点 A 的时钟,然后通过延迟 $$\Delta b$$ 的路径分配它。我们怎样才能避免产生负延迟的问题呢?请记住,时钟信号是周期性波形。假设期间为$$T$$。我们知道周期函数 $$f(t)$$ 的周期为 $$T$$ 满足

f(t)=f(t+T)$

应用负延迟 $$- \Delta b,我们有

f(t-\Delta b) = f(t+T-\Delta b)

因此,我们可以应用 $$T- \Delta b$$ 的正延迟,而不是应用 $$- \Delta b$$ 的负延迟。如下图 3 所示;请注意,图 3 显示了 DLL 应用于原始时钟信号的延迟,与图 1 形成鲜明对比,图 1 显示了从 A 到 B 以及从 A 到 C 的路径引起的延迟。

图 3. 对于周期性信号,适当的正延迟可以像负延迟一样发挥作用。图片由Xilinx提供。

基于 PLL 的时钟相差校正

我们可以不使用DLL,而是使用PLL来有效消除时钟分配网络的延迟。图 4 对此进行了说明。

图 4. 基于 PLL 的时钟去偏。图片由Xilinx提供。

在这种情况下,使用“压控

振荡器”而不是“可变延迟线”。反馈环路调整振荡器的频率,使得两个时钟信号CLKIN和CLKFB具有对齐的边沿。

我们可以轻松稳定 DLL 的反馈环路;然而,PLL 的情况并非如此,因为时钟分配网络将位于 PLL 的反馈环路内。这就是为什么基于 DLL 的结构更容易适用于时钟偏移应用。另一方面,PLL 在合成新时钟信号时更加灵活。

根据我们的讨论,我们可以使用 FPGA 的 CLB 来消除图 1 的时钟分布偏差,如下面的图 5 的简化框图所示。请注意,CMB 不仅可以对分布在 FPGA 内的时钟信号进行去偏斜处理,还可以对前往板上其他设备的时钟进行去偏斜处理。

图 5.使用 CLB 执行时钟去偏。图片由Xilinx提供。

我们看到 CMB 可用于合成新的时钟信号。现在,让我们看看另一组与时钟相关的 FPGA 资源:可用于在 FPGA 中分配时钟信号的专用缓冲区和路由。

时钟相关的缓冲区和路由

这些资源负责分配低偏斜的高扇出时钟信号。详细了解这些缓冲区和路线可能会让人不知所措,但我们将简要回顾一些重要的概念。为了以相等的传播延迟将时钟信号分配到

芯片的所有部分,我们可以使用一种特殊的路由形式,称为H 树。您可以在图 6 中看到一个示例。

图 6. H 树。图片由IEEE提供。

您可以轻松验证从 CLK-in 到每个矩形(代表时钟元件)是否有类似的路径。因此,理论上,所有时钟元件都会看到相同的时钟信号。图 7 显示了一些 Intel FPGA 用于分配全局时钟信号 (GCLK) 的 H 树。

图 7.图片由ACM提供。

GCLK 在整个器件中进行驱动,并充当自适应逻辑模块 (ALM)、数字信号处理 (DSP) 子电路、嵌入式

存储器和 PLL 等功能块的低偏斜时钟源。

除了 GCLK 之外,Intel FPGA 中还有区域时钟 (RCLK) 网络。如图 8 所示,这些 RCLK 仅被驱动至芯片的一个象限。

图 8.Intel象钟网络。图片由ACM提供。

Intel 设备还具有分布在芯片较小区域中的外围时钟 (PCLK) 网络。下面的图 9 显示了一个示例。

图 9. Intel 外围时钟。图片由ACM提供。

现在,覆盖所有这些网络,我们得到如图 10 所示的网络。

图 10. Intel FPGA 的时钟网络结合了 GCLK、RCLK 和 PCLK 网络。图片由ACM提供。

如图 8 和图 9 所示,FPGA 具有仅分布在芯片的一个区域中的专用时钟路由。这些称为时钟区域。请注意,不同的设备具有不同的时钟区域。另请注意,我们需要一些缓冲区来沿着我们上面讨论的专用路线有效地分配时钟信号。您可以在器件数据表中找到详细信息,图 11 显示了一个示例。该图显示了 Xilinx 7 系列FPGA 的一个时钟区域。BUFG、BUFH和BUFR是图中所示的三个与时钟相关的缓冲器。

图 11. Xilinx 7 系列 FPGA 的每个时钟区域都有多个与时钟相关的缓冲区。图片由Xilinx提供。