在电子系统设计中,电源 - 信号协同仿真至关重要,而 SSN(同步开关噪声)是其中一个关键问题。产生 SSN 的主要机制有三种,分别是感性串扰、δ - I 噪声和电源压缩。

当所有驱动同时切换时,便会产生 SSN 噪声。从攻击信号到受害信号的相互耦合以及与电源和接地路径的电感相关的 δ - I 噪声,是在攻击信号上升 / 下降时间产生噪声的主要机制,侵害信号的 di/dt 是造成这种噪声的根源。水平结构(传输线和面)和垂直结构(电线、球和过孔)都会产生 SSN 串扰,如下图所示:

电感耦合通常是 SSN 的主要机制。当来自一个导体的电流产生磁场时,该磁场会与另一个导体耦合并在其上产生电压,其方程为:

其中 m 是侵害信号和受害信号之间的互感。需要注意的是,当驱动电流恒定时,感性耦合不会发生,只有当电流随时间变化时才会出现。与攻击

驱动器相关的导体在信号波形的上升和下降时间内产生磁场模式的变化,并将噪声电压耦合到受害导体。感性耦合的大小与攻击信号和受害信号的平行长度成正比。在实际的电路设计中,合理布局导体的平行长度,能够有效降低感性串扰带来的影响。

当大量电流试图通过少量导体进入或退出封装时,就会产生 δ - I 噪声。当许多驱动器从高电平切换到低电平时,信号电流进入信号引脚,必须通过地引脚退出;同样,当这些驱动器从低电平切换到高电平时,电流必须通过电源引脚进入。其方程为:

式中 L 为与电流路径相关的电感,通常以功率路径或地路径的自感为主。和感性耦合一样,δ - I 噪声仅在信号转换期间发生,因为这是电流作为时间函数变化的时间。当驱动电流恒定时,δ - I 噪声不会发生,因为没有 di/dt 产生噪声。在高速电路设计中,需要充分考虑电流路径的电感,以减少 δ - I 噪声的影响。

电源压缩噪声是设备内本地电源和地之间电压的变化。电源和地之间的电压差使电路能够执行其任务,而这种变化会影响硅的性能。

当输出缓冲器改变其状态时,输出结构将瞬间构建从电源轨道到地的低阻抗路径。输出转换导致输出充电或放电,要求输出负载上的电流立即可用,以达到所需的电压水平。局部电容提供瞬态电流所需的存储能量,这降低了本地电压并从外部引入电流。流过电容的电流产生电压变化,其方程为:

电源压缩不会立即发生,而是在驱动器完成转换后很长时间内发生,只要电流流过电容。在电源管理设计中,需要合理配置电容,以降低电源压缩噪声对电路性能的影响。

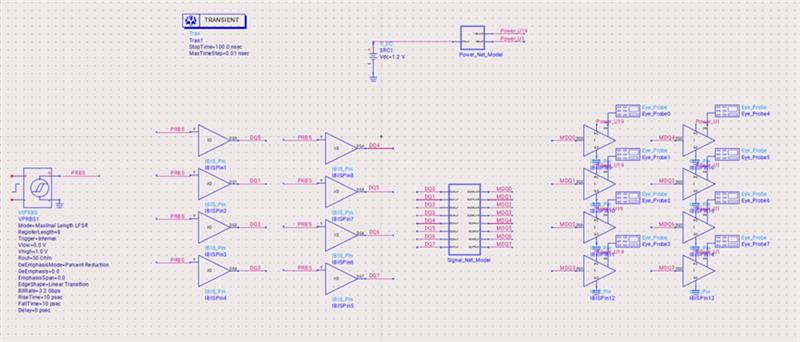

这里我们来看一个更加完整的:

Case1:储存芯片采用理想电源供电,原理图和结果如下:

Case2: 存储芯片采用 PDN 网络供电,电源和信号网络分开

Case3: 存储芯片采用 PDN 网络供电,信号和电源网络耦合在一起

Case4: 存储芯片采用 PDN 网络供电,信号和电源网络耦合在一起,存储芯片有抽电流负载

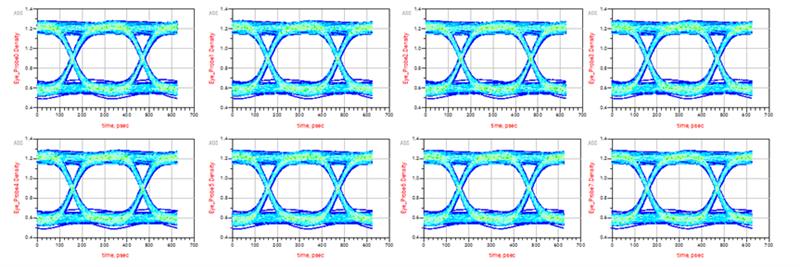

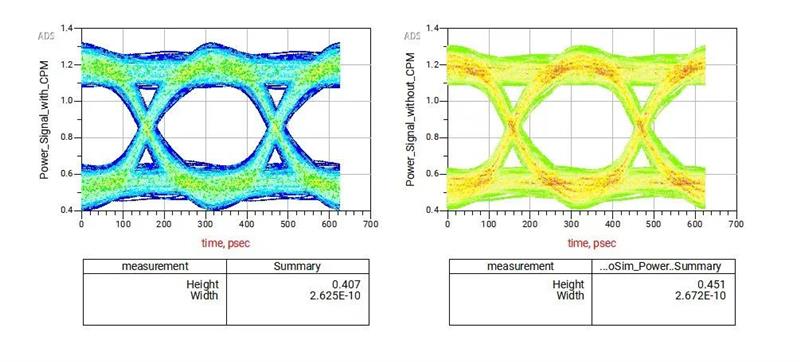

总结来看,信号和电源的耦合在存储芯片上更容易观察,主要原因有两个:一是存储芯片是并行接口,多个数据一起同时工作;二是存储芯片(DQ 信号)是单端信号,对噪声更加敏感。从 Case1 - Case3 我们可以明显看到电源对信号的影响,例如在低压大电流的场景、信号参考电源的场景等。Case2 和 Case3 说明电源和信号是整体耦合的,如电源噪声可以通过 GND 网络传递给信号,如下面的图片所示:

从 4 可以看到,负载的动态效应对信号也有影响。通过对这些的分析,工程师们可以更好地理解电源 - 信号协同仿真中的 SSN 问题,从而优化电子系统的设计。