数字设计师经常遇到的挑战之一是消除设计中的小故障。这通常是通过确保数据锁存时有足够的建立和保持时间来解决的。

“毛刺”是在整个时钟周期内不保持活动状态的信号。如果带有毛刺的信号馈送到多个锁存器的时钟线,则一些锁存器可能会被更新,而其他锁存器则可能不会。这显然是设计师想要避免的情况。还应该注意的是,传播延迟随温度变化,因此,在开发过程中不产生毛刺的设计可能在不同条件下产生毛刺。

通过在 Microchip 外设集中添加可配置逻辑单元 (CLC),终用户基本上可以“设计”可与 PIC

微控制器连接的简单外设。由于能够将信号驱动到 PIC 器件中,从而导致中断和递增

计数器,因此有必要提供一些指令,以便可以使用 CLC 外设创建稳定的设计。

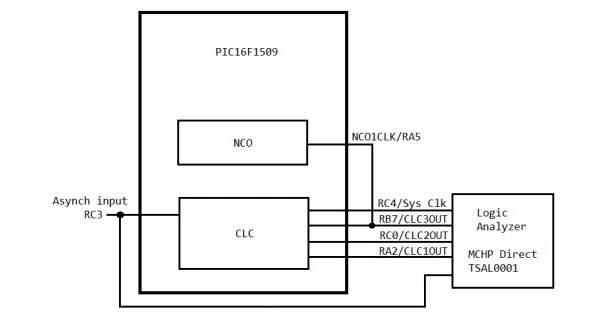

本示例使用 PIC16F1509,它使用四个可用 CLC 模块中的三个。第四个 CLC 模块用于将内部 FOSC 信号路由到 RC4 引脚,以便可以用逻辑

分析仪查看。CLC 内部的其他信号(XOR 输出、锁存器输出)已在外部引脚上输出,以便更清楚地了解应用程序的运行情况。

框图(图 1)显示了 RC3 上的异步输入信号以及为

逻辑分析仪供电的 CLC 输出。CLC3 信号是我们的无干扰时钟信号,被馈送到 NCO1CLK 焊盘。

图 1 无故障框图 –

工作台设置

在此示例中,我们将创建一个高速计数器,用于递增 NCO 寄存器。只要外部脉冲信号为高电平,NCO 就会递增。这创建了一个高分辨率、长持续时间的计数器,因为 NCO 计数器是一个 20 位宽的寄存器。读取数据和重置计数器大约需要 16 个指令周期(16 MHz 时钟为 4 ?s),因此脉冲之间必须有至少 4 ?s 的低电平时间。CLC2 上的下降沿中断标志提供脉冲宽度测量已完成的信号。虽然 NCO 寄存器被设计为能够抵抗时钟输入上的毛刺,但将干净的信号馈入 NCO 时钟线仍然是良好的设计实践。

该电路的个设计确实允许毛刺传入,并且是脉冲信号与系统时钟的简单“与”。请注意,当脉冲信号在时钟下降之前不久上升时,时钟上的尖峰是如何产生的(图 2)。

图 2 异步脉冲和系统时钟的逻辑“与”