如今,音频接口已经变得无处不在。它适用于工业物联网 (IIOT) 的大多数单板计算机 (SBC)。有多种类型的可用接口,从模拟音频端口到数字音频端口。每种类型的接口在设计和测试方面都有其自身的挑战。在组装和生产过程中对这些接口的测试涉及从模拟或数字前端到处理单元的数字音频输入端口的完整路径。

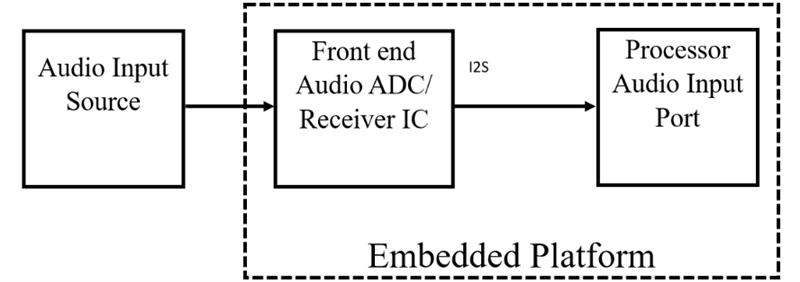

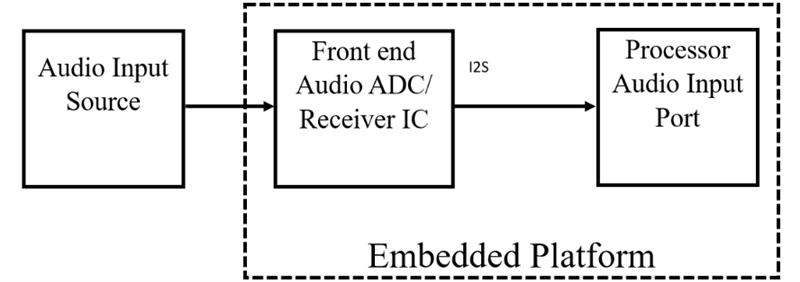

嵌入式平台上的音频前端和生产测试设置环境中音频数据路径的通用流程如下所示(图 1),

图 1:嵌入式平台的测试设置和音频前端()

上图显示了数据路径中存在的主要块/组件。所提供的接收器 IC 可以是模拟前端 IC,例如模数

转换器 (ADC),也可以是数字音频接收器 IC。IC 的输出可以是任何串行格式,例如 IC 间声音

总线 (I2S)。该接口可以传输脉冲编码调制 (PCM) 格式的原始音频数据。

生产测试的目的是确保完整的音频路径针对各种问题进行功能测试。可能的问题可能包括以下内容:

前端接收器 IC 故障。

I2S 线上的组装相关问题,例如固定在高电平(连接到

电源)或固定在低电平(连接到接地)或多条信号线之间的短路。

该音频接口测试将成为更大的生产

测试系统的一部分,该系统将测试嵌入式板上的所有接口。

下面列出了一种用于检测音频接口测试中与组件相关的问题的常用技术。对于前端接收器 IC 故障,需要使用不同的技术,但这些技术超出了本文档的范围。

技术 1 – 主观测试 主观测试包括捕获几秒钟的音频数据样本,并将其与听力检查所播放的实际音频进行比较。该技术的缺点是需要人工干预且耗时。例如,如果有多个立体声通道,则用户需要逐个收听并确认。

考虑到上述技术的缺点,我们提出了一种创新的方法来测试音频接口信号并使整个过程自动化。

技术 2 – 自动化测试 要了解这种自动化测试技术,了解 I2S 接口的一些基本概念非常重要。

I2S有三个信号——BCLK(位时钟)、WCLK(字时钟)、DATA(数据信号)。如果 BCLK 或 WCLK 不正确(卡在高/低),则处理器音频输入端口将无法捕获,并给出相应的结果,显示时钟故障。如果这些信号良好,则无论 DATA 的值如何,都会发生音频捕获。现在,如果 DATA 停留在 1 或 0,则音频数据缓冲区将包含每个 16 位样本的全部 FFFF 或全部 0000。因此,当我们生成MD5校验和时,我们将得到两个对应的值:MD5(FFFF)和MD5(0000)。对于音频数据的每个其他值,MD5 校验和都会不同。这个概念可用于自动化和检查音频捕获信号。

此方法的过程是在正确播放音频且未处于静音状态时捕获音频。这将确保我们的音频文件仅被捕获并且缓冲区中的数据是正确的。一旦音频数据缓冲区捕获了大约 100 个样本,就可以生成其 MD5 校验和。如果 DATA 信号处于高电平,则其 MD5 校验和值将与 MD5(FFFF) 相同,如果它处于低电平,则其 MD5 校验和值将与 MD5(0000) 相同。如果 DATA 信号正在切换,则 MD5 校验和值将是任何其他随机值。因此根据MD5校验和值,我们可以得出DATA信号是否有问题的结论。

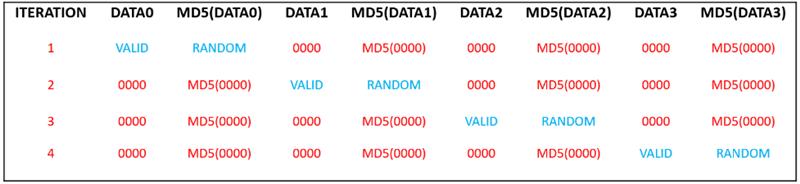

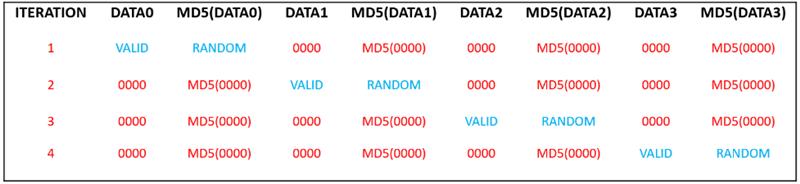

通常,这些 I2S 线会有多个数据信号。我们可以通过以下带有四个数据信号 DATAx (x = 0,1,2,3) 的 I2S 总线示例来演示这一点。这可以通过在 DATA 信号之一上提供音频数据并为所有其余数据信号提供 0 来完成。这样我们就可以生成所有 DATAx (x = 0,1,2,3) 捕获数据的 MD5 校验和,并确认 MD5 校验和值符合预期。

如果我们仅在 DATA0 上给出音频数据,则 DATA1-3 信号的 MD5 校验和应为 MD5(0000),对于 DATA0,它应为某个随机值。这可以在四次迭代中依次对所有四个数据信号完成,如表 1 所示。

表 1:音频测试的迭代()

该技术的局限性在于它只能用于识别上述问题。对于某些用例,它无法区分问题。例如,如果多条信号线短路,那么该技术可以检测到存在问题,但无法清楚地说出哪些线短路在一起。