2 、实现方法

现场可编程门阵列(FPGA)具有体系结构和逻辑单元配置灵活、集成度高以及设计开发周期短等优点,因此,选用FPGA来验证并实现本滤波器结构。VHDL是一种硬件描述语言,主要用于描述数字系统的结构、行为、功能和接口,与FPGA相结合后,表现出更加强大与灵活的数字系统设计能力。用VHDL完成数字系统的功能描述,用FPGA来实现是一种实用方便的软、硬件结合方式。从硬件描述语言到FPGA配置数据文件是由综合工具以及布局、布线工具来完成的。数字系统的功能终能否实现以及性能如何,取决于数字系统的算法结构,也取决于综合工具、布局和布线工具,还有器件性能。但是,如果数字系统的算法设计不好,就会有更多的设计反复。这里对FIR滤波器提出一种处理时间和所用芯片面积可以互换的结构,在初的设计时,就能对其处理能力有所估计,减少了设计的反复。

对于FIR滤波器,Xilinx提供了两个软核,一个是基于分布式运算的,另一个是基于单路的乘加运算。对于大阶数、高采样率的滤波器,这两种滤波器结构都不太适合。

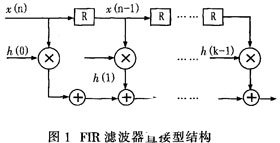

为了提高FIR滤波器的吞吐量,可用并行加流水线的结构来实现FIR滤波器,如图2所示。流水结构用于提高吞吐量率,并行结构可以减小处理延时。利用流水和并行结构调整滤波器性能使其满足实际应用要求。这里实现三级流水和二路并行的FIR滤波器。三级流水分别对应取数、乘法和累加。主要由双口RAM、乘法器、累加器、控制逻辑和流水线间的寄存器组成,还有数据写入模块(图中未画)。

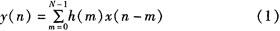

用两块RAM分别存放FIR系数和数据的前N个样值点,这两个RAM要求有一个写数据和一个读数据的双端口RAM。数据写入模块负责把所要滤波的数据轮换地写入两个双口RAM;FIR的系数也按偶数下标和奇数下标分别写入两个系数RAM,实现时是预先配置的。在实现滤波时,如图1所示对数据移位是不现实的。因此,用交联网络结合控制模块实现级流水--取数,完成给下流水线正确送数的目的。第二级流水是两个并行的乘法器,完成乘法运算。第三级流水是一个累加器;在控制逻辑的控制下,对乘法器输出结果进行正确的累加运算。

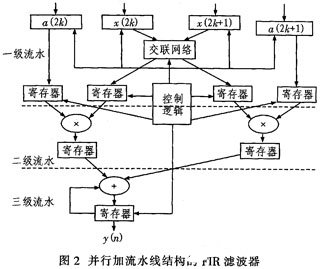

完成结构设计后要进行时序设计。数据写入模块的时钟是根据数据源产生数据的速率而定的。而流水线的工作时钟频率要求大于数据产生时钟频率的N/2倍,N是滤滤器阶数,2是并行度。也就是要求流水线在数据产生的一个周期内能完成FIR滤波器输出的计算。其中的控制逻辑是流水线正常运行的关键。数据流水线上的各种时序要求都要由其产生,包括读数据地址、读系数的地址、交联网络的控制和流水线结构的输出。其VHDL的端口描述如下:

系数地址由计数器产生,计数器周期是滤波器的阶数除以并行度,由first_data_address的第0位的边沿触发,以重新从0开始计数。数据RAM的地址加上计数器的值。两个RAM地址因当前输入滤波数据的存放位置,可能相同也可能相差1。交联网络的控制信号是计数器的位。累加器输出的使能信号是在计数到滤波器的阶数时产生的,而后经过延时给到累加器。累加器清零信号在这里产生要比累加器中用其他方法方便得多。

交联网络也是设计的重点。对于并行处理结构,各单元之间数据的共享和通信是限制并行度的主要原因。在并行度为2的结构中,只要轮流交换系数就可以了。但是对更高的并行度,这一通信网络的延时是相当大的,这也是把它单独列为滤波器的流水线的的主要原因。

还要注意的是:有符号数常用补码表示。在对有符号数进行扩展时,要扩展位。对乘法器的输出一般要进行扩展,以避免累加器溢出。

对于乘加运算,有一种分布式计算方法,也就是把乘法进一步分解为部分和(二进制系数的每一位和输入数据相与的结果)。当乘加运算的一个乘数是已知常数时,分布式乘加运算会很节省资源。因为系数固定,与运算的结果是在运算前可知的,这样零位与数据相与的结果是不参与加运算的,从而实现无乘法器的滤波器。这里不选用这种方法,原因有二:其一,分布式运算将使滤波器难以重配:其二,基于FPGA的硬件乘法器较综合得来的乘法器性能更佳。

3、 仿真及测试

用VHDL语言描述全部电路模块后,输入系数1、2、3、4、5和数据-l、-2、3、4等进行测试.用Mod-elsim进行仿真,其结果如图3所示。

可以看出,模块能正确进行计算,从数据输入到数据输出约延时2个数据时钟.这主要是前面的数据输入模块的延时。乘加部分采用数据时钟的N/2倍,其延时与滤波器的阶数成比例,但不会超过一个数据时钟周期。

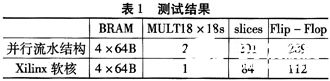

然后,对VHDL描述就Xilinx的Spartan-3进行综合和测试。可以得出表1所示的测试结果,其中行为并行流水结构所设计的滤波器,第二行是采用Xilinx提供的软核设计的滤波器。

可以看出,除了增加一个乘法器外,逻辑块和触发器都增加了一倍多。用这种结构设计的滤波器面积增加了一倍,速度性能也提高了一倍。以上两种滤波器可以应用在语音信号处理中--让语音信号通过低通滤波器以获取语音的低频分量。相对而言,并行流水结构能实现比Xilinx软核更高阶数的滤波器。在听觉上,经过两种滤波器(相同阶数)的语音信号没有太大差别。

4、 结束语

本文在运算层次上,依据流水和并行运算结构实现直接型FIR滤波器。如果在设计滤波器时,结合级联型和直接型两种滤波器结构,那么也能实现同样的并行和流水的效果。实际上,还可在更低层次的乘法运算时,对部分和也用并行和流水结构来实现。这些结构的选择都依据性能要求和实现的复杂性来具体确定。

作为实现现代高性能处理器的方法,并行和流水结构各有特点。并行是以面积换速度。流水是以延时换速度,采用这两种结构,就能在面积、速度、延时之间灵活互换。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。