用于Delta-sigma数据转换器的抗混滤波器设计方案明显不同于SAR(逐次逼近寄存器)或流水线(高速)转换器的设计方法。拥有SAR或流水线转换器,您即拥有了每次评估一个样本的系统。无论是哪种情况,都可以“抓住”模拟信号,并将其储存于转换器的输入电容阵列。这些转换器评估已存储的信号,并为各个样本提供一个数字表达。对这两款器件,多阶抗混滤波器的目标频率即是该转换器的奈奎斯特频率。

在高采样率(FS,参考1)下,delta-sigma转换器的输入调制器会对输入模拟信号进行多次采样。而后续的Sinc数字滤波器会对一组此类调制器样本进行再次采样,并转换为一个输出的数字表达。从一个调制器的样本串到一个24比特的数字码,这个转换过程要比delta-sigma输入结构的采样速率慢得多(FD,参考1)。因而,delta-sigma转换器有两个采样率(FS,FD)。但是,一阶抗混滤波器的目标频率是输出数据速率FD.在参考1中,您可以找到delta-sigma转换器的基本抗混滤波器设计概念。

请注意,参考1和参考2中的电路和论述方法仅解决了减少差分噪声问题,而无关转换器的输入阻抗或共模噪声。

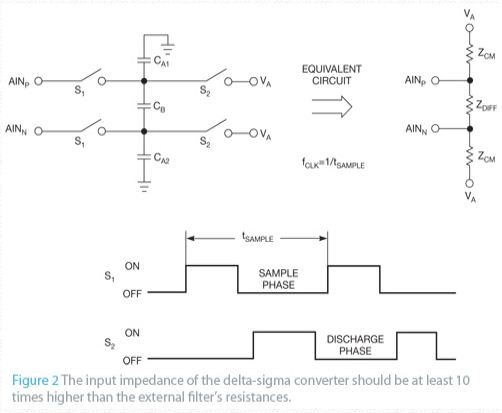

对于转换器的输入阻抗,在测量AINP和AINN之间的电压期间,delta-sigma转换器开关电容输入端的电容器会连续地充电和放电。与外部电路相比,这些内部电容(CB、CA1及CA2)相对较小。因而,其平均输入阻抗显示为阻性。转换器的电容值和调制器的转换速率决定了这一电阻值。

测量图2中结构的共模输入阻抗时,需将AINP与AINN接到一起,并测量转换期间每个管脚消耗的平均电流。测量差分输入阻抗时,需给AINP与AINN施加一个差分信号,测量从管脚流至VA的平均电流。共模和差分电阻的范围为几百千欧姆至几百兆欧姆。其数值取决于转换器内部输入开关电容结构后面跟随的电路。RFLT/2的值必须比转换器的输入阻抗低至少10倍。

两只共模电容CCM_P和CCM_N用于衰减高频共模噪声。差分电容至少应比共模电容大一个数量级,因为共模电容的失配会导致差分噪声。

如果进入任何ADC的输入信号中包含有高于一半数据速率的频率,即会发生混淆现象。为防止此现象的发生,应对包含噪声和干扰成分的输入信号进行频带限制。Delta-sigma转换器中的数字滤波器可提供一些高频噪声衰减功能,但是数字sinc滤波器不能完全代替抗混滤波器。在设计一个输入滤波器电路时,要考虑转换器过滤器网络和输入阻抗之间的相互作用。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。