1.引言

下面来介绍一种实现系统芯片功能测试的方法。

2 评估测试需求

先要审定系统芯片测试的基本要求,并明确解决如下4个问题闭:1)哪些是必须的基本测试能力;2)怎样观察对测试序列的响应;3)测试平台需要多高的灵活性;4)需要多少经费和时间。

对基本测试平台能力[3]的评估应该包括:1)所需的激励时钟速度;2)所需的激励通道数;3)输入的电压标准;4)测试序列的长度。

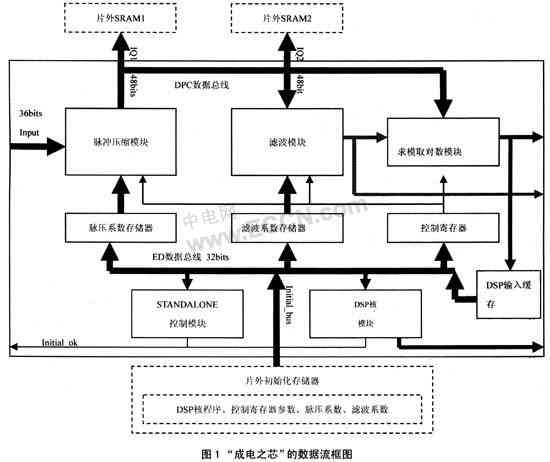

“成电之芯”是一款0.18μm工艺、内嵌DSP核的730万门SoC,面积31mm×31mm,PBGA609封装,该芯片的数据流框图如图1所示。

|

图1中,实线区域为芯片内部各模块,虚线部分为片外存储器。从图中可以看出,雷达信号处理专用芯片的数据传输主要由DPC数据总线和ED数据总线完成。

通过上述对“成电之芯”的简单介绍,该芯片的系统功能和测试平台的能力需求已经一目了然。

3 功能测试平台的建立

3.1 功能测试平台建立方法

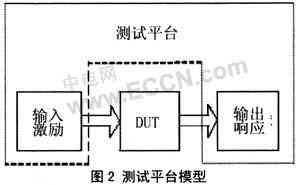

测试平台是为了向被测芯片施加输入激励而建立起来的。如图2所示,测试平台向被测芯片输入激励,对输出采样,并将结果与期望值比较,得出比较分析结果。

|

建立测试平台的过程是建立在对被测芯片功能属性透彻理解的基础上的。目前,常用的测试平台建立方法有:采用可编程器件建立测试平台、基于波形建立测试平台、基于可编程测试仪建立测试平台和基于事物建立平台。

3.2 功能测试平台的构建

本设计的功能测试主要采用基于可编程器件建立测试平台。

从图1可以看出,“成电之芯”主要有以下几类接口:36位的输入信号总线Input;32位的初始化数据总线Initial_bus;48位的片外缓存数据总线IQ1和IQ2;28位的求模或取对数输出总线Log_out;56位的滤波结果输出FIR_I_OUT(28位)、FIR_Q_OUT(28位;16位的HD数据总线。

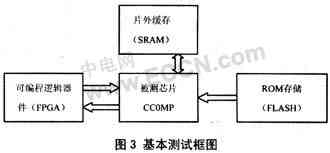

根据基于可编程器件建立测试平台的设计思想,功能测试平台的构建方法如下:采用可编程逻辑器件进行输入激励的产生和输出响应的处理;采用ROM来实现DSP核程序、控制寄存器参数、脉压系数和滤波系数的存储;采用SRAM作为片外缓存。基本测试框图如图3所示。

|

根据“成电之芯”的要求,芯片需要外部提供136 k 32bit的存储空间为其提供脉压系数和滤波系数,同时需要其它的一些存储空间为芯片存储片外的DSP核程序和控制寄存器。

由于做MTD滤波时,每个相参处理间隔的数据量为2M深度,所以片外必须准备两片深度为2M,数据宽度为48位的SRAM作为芯片的片外缓存。

除此之外,芯片需要外界输入数据和控制信号,并且需要接收芯片的输出数据。这部分的功能可通过可编程逻辑器件来完成。

通过以上分析,CCOMP芯片功能测试平台选用了两片SST39VF3201来做它的片外初始化存储器、6片GS832018来做它的片外缓存、一片XC3S5000来产生它的时序控制信号以及和外部接口的控制逻辑、两片MT48LC4M32用做它的输出缓存、两片SST39VF3201来做它的输入数据存储器,另外还选用了一个AD和一个DA芯片来实现与外界的数据通信。实现框图如图4所示。

|

4 测试平台的实现

4.1软件的实现

根据“成电之芯”输入激励和输出响应的数据对比要求,编写了可综合的verilog代码。代码的设计完全按照“成电之芯”的时序要求实现。

4.2 硬件的实现

根据功能测试平台的实现框图进行了原理图和PCB的设计,设计完成了一个可对“成电之芯”进行功能测试的系统平台。实物图如图5所示。

|

5 结论

本文通过对“成电之芯”功能测试平台的设计与实现,阐述了一种基于可编程逻辑器件的系统芯片功能测试平台的建立。本文从系统芯片的测试评估出发,一步步深入系统芯片测试方法分析,终实现一个完整的测试平台。

该系统除了阐述功能测试平台的实现方法外,同时也对待测芯片——“成电之芯”进行了充分的测试,为每一块芯片的功能是否完好提供了重要依据。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。