DM642作为高性能的视频处理芯片,被广泛应用到视频处理的很多领域,但是DM642的I2C应用容易遇到I2C、VP等死锁,以及SAA7115的从地址不能正确设置的问题。本文主要介绍的就是基于DM642的视频采集处理系统中I2C模块的正确初始化,以及通过I2C总线正确地对视频解码芯片SAA7115的寄存器读/写程序。

1 I2C总线控制器的初始化

I2C总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。I2C总线产生于在80年代,初为音频和视频设备开发,如今主要在服务器管理中使用,其中包括单个组件状态的通信。例如管理员可对各个组件进行查询,以管理系统的配置或掌握组件的功能状态,如电源和系统风扇。可随时监控内存、硬盘、网络、系统温度等多个参数,增加了系统的安全性,方便了管理。

为了正确使用DM642内置的I2C模块,首先需要正确的初始化。

1.1 解锁DM642中的I2C模块

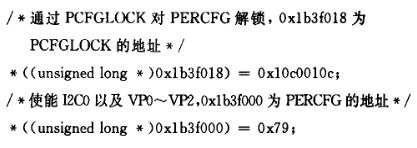

在DM642的I2C应用中,容易遇到不能使用初始化I2C模块的问题,原因在于没有先解锁并使能I2C模块。在DM642的数据手册中可以看到,复位后I2C模块是处于锁定禁止状态的。也就是说,在硬件配置寄存器PERCFG中的I2CoEN位为0,所以在初始化前要在配置I2C模块控制寄存器之前,使能I2C模块。但是,如果要修改PERCFG中的内容,就要先向PCFGLOCK中写入0x10C0010C,对PERCFG解锁。通讨加下程序使能I2C模块:

1.2 I2C模块的时钟选择

I2C总线主要的优点是其简单性和有效性。由于接口直接在组件之上,因此I2C总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。总线的长度可高达25英尺,并且能够以10Kbps的传输速率支持40个组件。I2C总线的另一个优点是,它支持多主控(multimastering), 其中任何能够进行发送和接收的设备都可以成为主总线。一个主控能够控制信号的传输和时钟频率。当然,在任何时间点上只能有一个主控。

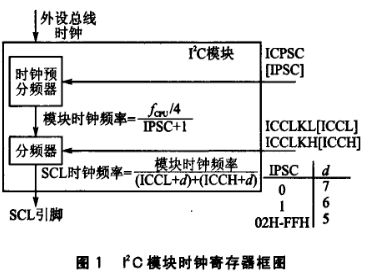

在使能I2C模块后,就可以对其控制寄存器进行初始化了。CPU时钟频率为600 MHz,I2C模块规定模块时钟频率必须在7~12 MHz中选值,所以设定I2C模块时钟频率为10 MHz。由图1中的计算公式可得:IPSC为OEh。由于DM642和SAA7115都支持I2C总线的400 kbps快速模式,根据IPSC的取值,由图1可知d=5。由此可以设定:ICCL=7,ICCH=8。

1.3 设置从地址时容易遇到的问题

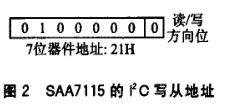

需要注意的是,在DM642的I2C应用中经常会遇到不能正确读/写从设备的问题。这是因为DM642对I2C模块的从地址寄存器设置不同于其他芯片的I2C应用。在标准I2C协议中,器件的7位地址格式要将地址和读/写方向位一同送入从地址寄存器。但是,DM642的I2C的应用中只需要向从地址寄存器中送入7位器件地址,读/写方向位由DM642自动生成。例如,SAA7115的标准I2C写从地址为40H,如图2所示。

标准I2C协议中包括21H的地址信息和1位(读/写方向位),DM642只需将21H送入从地址寄存器。如果送入40H,将会导致读/写错误。

2 I2C读/写软件设计

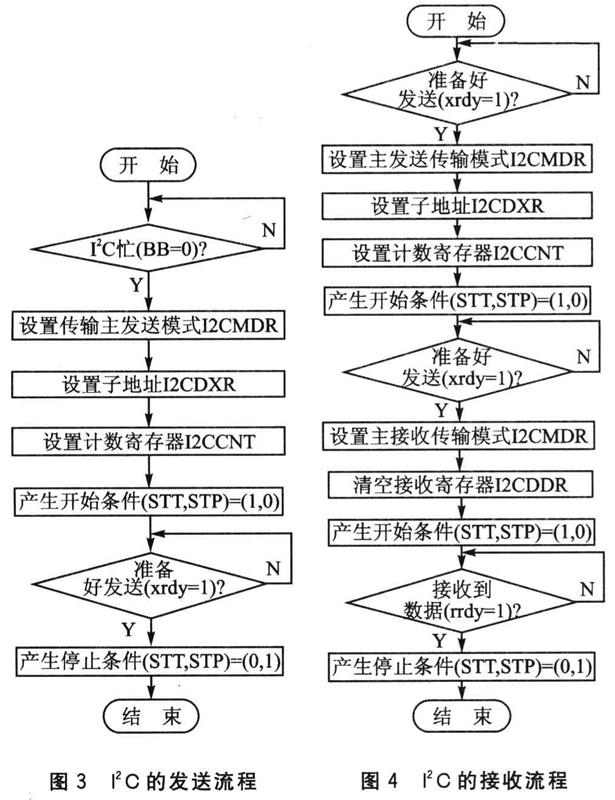

2.1 配置模式寄存器I2CMDR

对SAA7115的每个子地址操作后,其地址指针会自动增加,但是它的可配置寄存器的自地址并不是连续分布的。所以将I2C工作模式寄存器(I2CMDR)配置为计数模式。每次执行I2C_write()只传送数据,通过多次调用I2C_write()来完成SAA7115的初始化。先向I2CMDR写入4620H,当读取SAA7115的寄存器时,设置为无重复主接收模式,并向I2CMDR写入4420H。

2.2 配置从地址寄存器I2CDXR

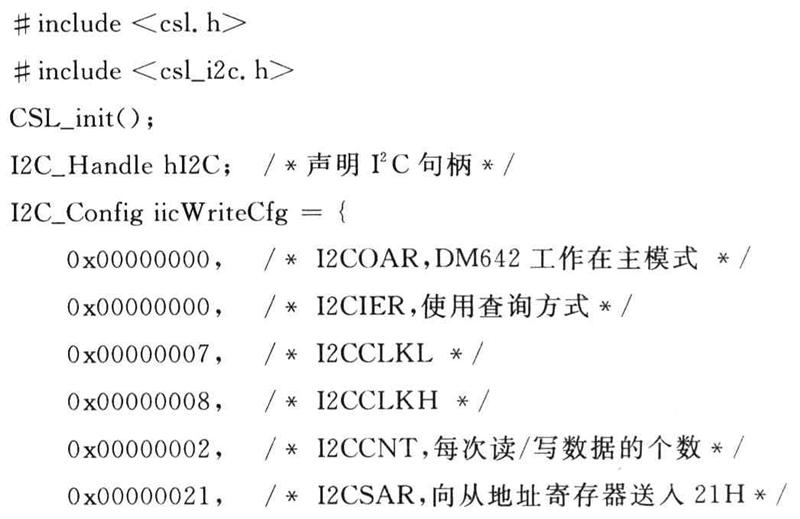

DM642对SAA7115的配置是通过寻址来实现的。当DM642向解码芯片SAA7115写数据时,通过I2C总线发送寻址指令,将右移位后的SAA7115的7位从地址写入I2CDXR寄存器。以下是初始化程序:

2.3 I2C对SAA7115的读/写程序设计

综上所述,图3和图4为DM642对SAA7115的读/写程序流程。

3 结 语

本文设计的程序经过运行证明,通过I2C总线控制寄存器的配置,DM642对视频解码芯片SAA7115读/写正确,完成了对视频信号输入制式、视频信号通道选择、视频数据输出格式、同步信号插入位置、亮度色度及对比度设定、同步信号输入开关、视频采集量化启动和关闭等内部寄存器的设置。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。