许多客户希望提供一种可以从802.16-2004升级到802.16e标准的方法。IEEE802.16标准的各个版本都规定了PHY(物理层)的多种选项,包括调制、信道编码和天线分集技术。物理信道带宽可以在1.25 MHz~20 MHz之间变化。上述所有选项都会影响基站的性能和信号处理复杂度,都要求基站的PHY采用可编程的信号处理器件。本文详细介绍用可编程DSP实现IEEE 802.16 PHY信号处理。

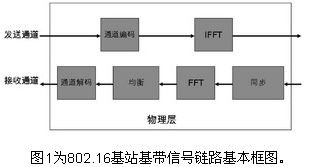

因为802.16-2004和802.16e标准都是在OFDM基础上建立的,所以FFT和IFFT起了很大的作用。这两种变换都用于频域副载波(携带编码的数据位)和时域采样(在物理通道上传送)之间的转换。IFFT的输出被称为一个OFDM符号。按照这种方式进行通信,OFDM系统可以实现抗多径干扰,各副载波之间几乎或者完全无干扰,并且具有相当低的复杂度。

与FFT密切相关的是信道均衡,它包括大量的MAC运算,还包括客户专用的复杂算法,以便恰当地估计信道和表征结果,尤其是在具有移动性的系统。

同步模块在测距期间起作用,基站通过此模块获得新用户的信号,并且调整现有用户的定时(通过反馈来调整)。同步通常是通过计算接收信号与已知前同步信号的相关性,或自动计算接收信号与其自身延迟信号的相关性实现的,利用该信号确定的周期性属性,然后将得到的相关性结果通过一个检测器,以便确定是否有信号送到,如果有,确定其定时。

802.16标准支持高数据速率(70 Mbps左右),有多种信道编码选项。必备方案是卷积码(在802.16-2004标准中,还要结合里德-所罗门(RS)码),卷积turbo码、turbo乘积码,以及802.16e标准中的低密度奇偶校验码都是可选的。

信道解码的高数据速率超出了传统DSP体系结构的能力。可能的实现方法有专用指令、硬件加速器和可编程逻辑器件。除了本身计算的高复杂度,基站体系结构必须具有相当大的数据带宽和存储器,以便支持更先进的解码方案。

人们期望基于802.16e标准的系统实现多天线处理,它增加了两级的复杂度。首先,信号链中的几个模块,特别是FFT和IFFT,必须为每个天线流都复制一份。其次,系统必须为不同的天线流计算出并选取适当的权重,以满足诸如信号干扰比的要求。

在802.16e系统中,允许在同一个OFDM符号中复用多个子信道(因此称为OFDMA),从而增加了对可编程性的需求。虽然802.16-2004系统通常不需要每次处理一个OFDM符号,但是802.16e增加了子信道、副载波和OFDM符号之间的复杂映射,包含了几种可能的排列。这就增加了更多的总控制码和存储器访问,并且提高了调度处理任务的复杂度。另外,应该有一种体系结构支持升级以便增加功能,例如混合ARQ(自动重传请求)和MIMO(多输入多输出天线处理)。

为基站PHY提供的可编程技术包括DSP、FPGA以及可重复配置的逻辑器件。DSP的优势就是C程序和低功耗,但是传统的DSP不具有上述一些算法所要求的计算密度。虽然FPGA可以达到上述算法所需要的计算密度,但是如果完全采用FPGA解决方案,其编程模式可能无法完全实现复杂的控制功能。可重复配置的逻辑器件试图通过由常用的异构处理元件组成的一种结构来发挥DSP和FPGA的组合优势,但是其技术的成熟度和编程的易用性还存在问题。

考虑到上述需求和当前的处理器发展情况,适合802.16基站PHY的合理解决方案是采用双重方法。对于基本的系统,完全采用DSP解决方案可以提供必需的计算资源,同时提供方便的编程模式。对于具有更宽的信道带宽或较多天线数量的系统,应当采用DSP和FPGA的组合方案。采用这种方法,PHY可以保持类似的编程模式,同时将一小部分计算量大的功能分配给FPGA,例如信道编码。这两种体系结构都具有增加功能、升级软件以及移植到新版本标准的灵活性。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。