本文主要介绍直接数字频率合成器的原理和特点,研究用DSP Builder实现正弦信号发生器的设计方法,继承了传统DDS信号源调频、调相迅速的优点,给出了查找表压缩优化方法。并应用Altera公司推出的DSP Builder和QuartusⅡ进行了仿真实现。实际结果表明,此设计方法在节约芯片资源的基础上达到了较高了。

l DDS的基本原理

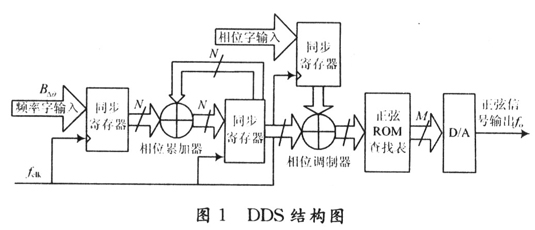

DDS的结构由相位累加器,相位调制器,波形存储ROM和D/A转换器组成。一个正弦信号发成器结构图如图1所示。相位累加器是整个DDS的,完成相位累加运算,它输入的是相位增量B△θ。加上一个相位偏移量,用于信号的相位调制。正弦ROM查找表完成相位到幅度的转换,它的输入是相位调制器的输出,也就是ROM的地址。

fo为输出频率,fo的值由fclk和B△θ共同决定:fo=fclk×B△θ/2N。DDS的频率分辨率△f用频率输入值步进一个间隔对应的频率输出变化量来衡量,即△f=fclk/2N(默认情况下,ROM存储整个周期信号波形)。可见,△f越小,DDS输出越高。

2 DDS改进方案

ROM查找表地址位数M越靠近相位累加器的位数N,相位寻址时舍去的位数就越小,相位舍位误差也就越小,但ROM表的大小会随地址位数M的增加成指数递增关系。为了使用较小的ROM而满足信号性能,必须采用优化方法压缩ROM。

2.1 正弦波特点

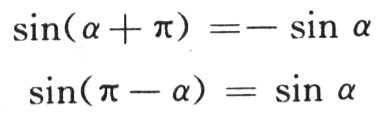

已知正弦波存在下面的关系:

由此可见,[π,2π]区间的波形可以通过[0,π]区间波形转化得到。进一步,由于[O,π/2]和[π/2,π]区间波形关于α=π/2对称,则[π/2,π],[π,3π/2],[3π/2,2π]三个区间波形都可以通过[0,π/2]区间的波形转化得到。

2.2 基于DSP Builder的ROM优化方案

从上面对正弦波特点的分析可得出,查找表ROM中只存储[O,π]或[0,π/2]区间的波形就可得完整周期的正弦信号。对于ROM中存储[0,π/2]区间波形的情形,将正弦波合成到[O,π]区间;位作为符号位,将正弦波合成到[0,2π]区间。图2给出了ROM中存储[O,2π],[0,π],[O,π/2]区间波形时,用DSP Builder实现正弦信号发生器的系统模型。

![ROM中存储[O,2π],[0,π],[O,π/2]区间波形时,用DSP Builder实现正弦信号发生器的系统模型](https://image.dzsc.com/data/2011/05/19/20110519170058453.jpg)

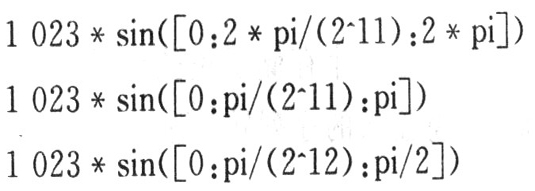

其中,PWORD为相位字输入,其值设置为O;AWORD为幅度控制输入,其值设置为50;adder为相位累加器;adderl为相位调制器。LUTl,LUT2,LUT3分别为存储[O,2 π],[O,π],[0,π/2]区间正弦信号的具有相同存储空间的ROM,它们模块参数“MATLAB Array”分别设置为:

另外,子系统controller的作用是,判断象限,将LUT3中正弦波合成到[0,π]范围。

2.3 仿真分析

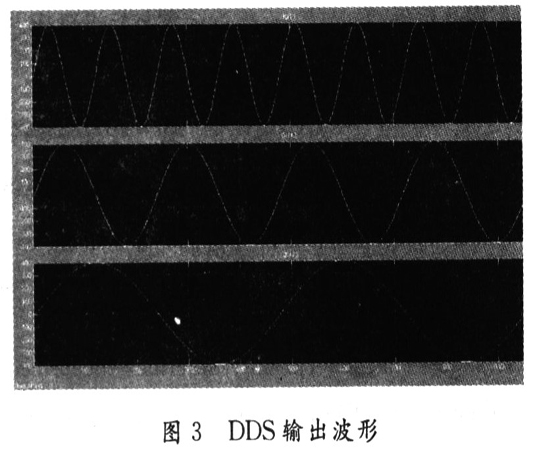

图3给出了图2系统模型中3个输出OUTl,OUT2,OUT3的波形。由图3可见,OUT2的频率是OUTl的1/2,而OUT3的频率是OUT2的1/2。由此知道有着相同地址输入的ROM,在存储空间大小相同情况下,存储正弦波区间越小,输出正弦信号的频率分辨率越高,即输出越高。所以,用相同的ROM,当存储1/4周期正弦信号时,合成的正弦信号有着较高的。

3 信号源的FPGA实现

Matlab/Simulink对设计好的DDS系统进行编译,通过调用DSP Builder的SignalCompiler工具可直接生成QuartusⅡ的工程文件,再调用QuartusⅡ完成综合、网表生成和适配,直至完成FPGA的配置过程。

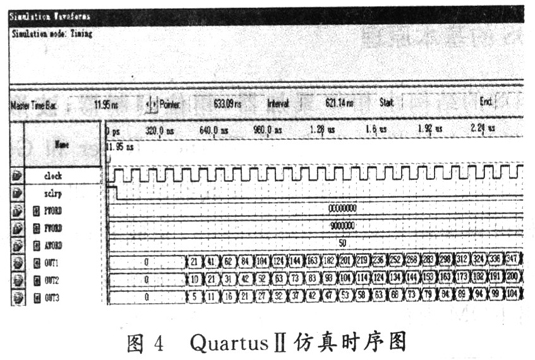

本设计方案采用的FPGA芯片是APEX20K系列器件EP20K200FC484。所得结果中的数字输出可以输出到SRAM芯片中,然后上载到计算机进行数字信号分析,模拟输出则通过HP示波器测试。图4给出了用QuartusII的仿真结果。仿真得到的3个输出OUTl,OUT2和OUT3与Matlab/Simulink中的仿真结果在相位、频率和幅度上基本一致。实验表明,利用FPGA所计设的DDS在满足性能的条件下,提高了输出的。

4 结语

本文介绍了一种改进了的基于DSP Builder的正弦信号发生器设计方法,应用APEX20K系列FPGA芯片实现。继承了传统DDS设计中的优点,使芯片在节约资源的基础上达到了较高的输出。

[1]. ROM datasheet https://www.dzsc.com/datasheet/ROM_1188413.html.

[2]. APEX20K datasheet https://www.dzsc.com/datasheet/APEX20K_1330793.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。