|

摘 要:介绍了TI公司的信号处理器TMS320VC5402串行口的主要特点,及其和音频模拟接口芯片TLC320AD50C的结构及其使用注意事项。详细讲述了两者的硬件连接及软件实现。

|

|

目前发展起来的高速数字信号处理器DSP在语音处理系统中得到了广泛应用。TMS320VC5402是TI公司生产的一种性能价格比较高的16位定点DSP。它的指令周期为10ns,具有运算速度快、通用性强、接口连接方便等特点,尤其适合在语音编码和通信中应用。

|

| 1 TMS320VC5402的McBSP TMS320VC5402有两个McBSP多通道缓存串行口。McBSP提供了全双工的通信机制,以及双缓存的发送寄存器和三缓存的接收寄存器,允许连续的数据流传输,数据长度可以为8、12、16、20、24、32;同时还提供了A-律和μ-律压扩,多达128个通道的发送和接收。McBSP通过7个引脚使得一个数据通路和一个控制通路与外部设备相连。数据经McBSP与外设的通信通过DR和DX引脚传输,控制信号则由CLKX、CLKR、FSX、FSR等四条引脚来实现。CPU和DMA控制器可以读取DRR1,2的数据实现接收,并且可以对DXR1,2写入数据实现发送。接收和发送帧同步脉冲既可以由内部采样速率产生器产生,也可以由外部脉冲源驱动。当FSR和FSX都为输入时FSXM=FSRM=0,外部脉冲源驱动,McBSP分别在CLKR和CLKX的下降沿检测,且DR的数据也在CLKR的下降沿进行采样。而当FSR和FSX都为输出时,则在CLKX和CLKR的上升沿进行检测。 16-bit的串行口控制寄存器SPCR1,2和引脚控制寄存器PCR用来配置串行口;接收控制寄存器RCR1,2和发送控制寄存器XCR1,2分别设置接收和发送的不同参数,如帧长度、每帧的数据长度等。 |

|

|

图1是当FSR和FSX为输出时McBsp的发送和接收时序图。另外,McBSP还可以通过R/XDATDLY 设置接收和发送数据延迟,通过R/XPHASE设置接收和发送的多阶段。

|

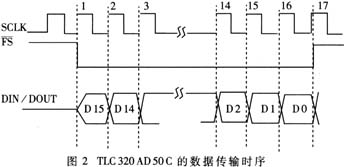

| 2 音频模拟接口芯片TLC320AD20C TLC320AD50C是TI生产的Σ-Δ型单片音频接口芯片。它集成了16位A/D和D/A转换器,采样速率可达22.05kb/s,其采样速率可通过DSP编程来设置。在TLC320AD50C内部DAC之前有插值滤波器,而在ADC之后有抽样滤波器,接收和发送可以同时进行。TLC320AD50C与TMS320VC5402之间采用串行通信方式,有两种数据传输模式:16位传输模式和15+1位传输模式。若采用15+1位传输模式,其中的D0位用来表示二次通信。TLC320AD50C的数据传输时序如图2所示。 |

|

|

该器件采用两组模拟输入和两组模拟输出,有足够的共模抑制能力,可以工作在差分或单端方式。当模拟输出时,输出端通常接600Ω的负载。

|

| 3 TMS320VC5402与TLC320AD50C硬件连接及软件实现 3.1 硬件连接 根据图1和图2的时序,则容易实现TLC320AD50C与TMS320VC5402的硬件连接,如图3所示。 |

|

| TLC320AD50C的MCLK外接8.192MHz的晶振,TMS320VC5402的FSX和FSR由TLC320AD50C设置。如果选择D7=0,N=8,则采样速率为8kHz。 3.2 通信协议 TLC320AD50C的通信有两种格式:通信格式和二次通信格式。 通信格式的16位都用来传输数据。DAC的数据长度由寄存器1的D0位决定。启动和复位时,缺省值为15+1位模式,一位要求二次通信。如果工作在16位传输模式,则必须由FC产生二次通信请求。 二次通信格式则用来初始化和修改TLC320AD50C内部寄存器的值。在二次通信中可通过向DIN写数据来初始化。 格式如下: |

|

|

|

系统复位后,必须通过DSP的DX口向TLC320AD50C的DIN写数据,如果采用一片TLC320AD50C,只需初始化其寄存器1、寄存器2和寄存器4。

|

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。