于专用

集成电路的出现,电流监测变得更加简单。电流监测集成电路随处可见,而且在大多数情况下效果很好,各种仪表

放大器也是如此,因此使用分立器件构建电流监测器似乎有些多余,但在某些情况下,使用分立元件的电路可能是方法,尤其是如果可以使用随处可见的低压部件。 本设计方案中的电路源于需要监控伺服系统 +180/180V 电源的两个电源轨中的电流。图 1显示了用于监控负电源轨的电路的相关部分。监控正电源轨的电路用 pnp 器件代替了 npn。使用廉价的双

晶体管和 1% 电阻来设置 Iref 以及 Re1 和 Re2 可获得效果。Rsens应为 0.1%,并充分考虑功率耗散。

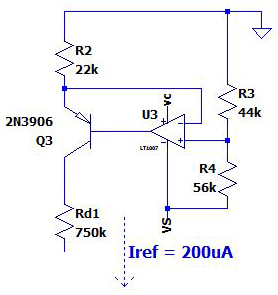

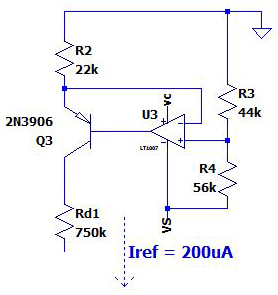

图 1负电源轨监控电路

这种电路以及所有使用这种拓扑的电路的灵感源自电流镜拓扑和以下概念:Rsense 中的变化电流以及因此 Rsense 两端的电压会以线性方式改变 Re2 中的电流以及因此 Rc1 两端的电压。

图 1 中的电路的实用性归功于 Re1 和 Re2。使 Ireffairy 非常小,使 Re2 和 Re1 非常大且值相等,可增加发射极电压相对于 Rsense 两端电压的相对值。这反过来又降低了当负载在无负载和满负载之间变化时输出器件的 Vce 的变化。

因此,通过合理选择 Iref、Re1、Re2、Rc2 和 Rc1,可以防止 Q2 进入饱和状态,同时不会超过晶体管的工作电压。请记住,hoe=I(集电极)/VA (早期电压)意味着减少 Icals 的变化会减少 β 的变化,从而改善线性度。Rc是 Rc1 和 Rc2 的总和,因此 Rc1/Rc 比率决定了无负载时 Vout? 处的偏移量。满载时 Rsense 上产生的电压决定了 Re2 和 Rc1 中电流的变化,因此决定了 Vout? 处的满量程输出。一旦确定了 Iref 的值,计算 Rc 和 Rd 上所需的无负载电压就很简单了。通过使用发射极电阻,变化的 Vce 对 Q2 的 β 的影响显著降低,并且检查模拟数据表明 β 的变化对负载电流和输出电压之间的相关性的影响相对较小。从所获得的结果来看,使用类似于威尔逊电流镜的配置可能是不必要的。 图 2 和图 3显示了恒流源产生 Iref 的替代方案。如果 Vss 稳定且无纹波,则可以省略恒流发生器,并可以选择 Rd 的值来提供 Iref。

图2恒流源产生Iref的替代方案。

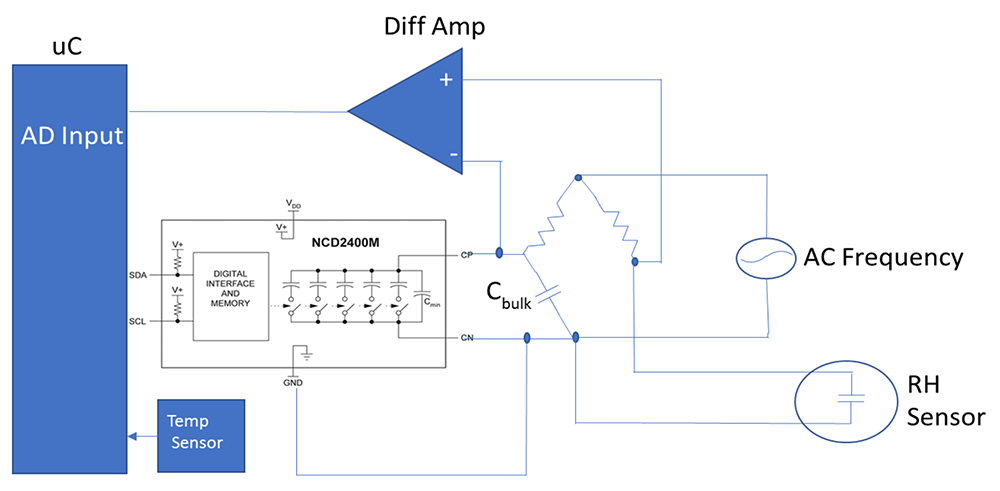

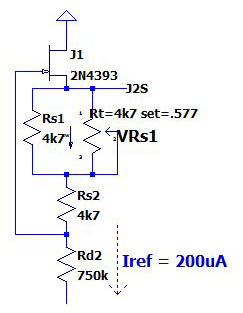

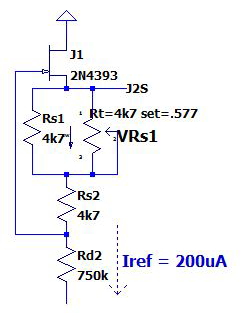

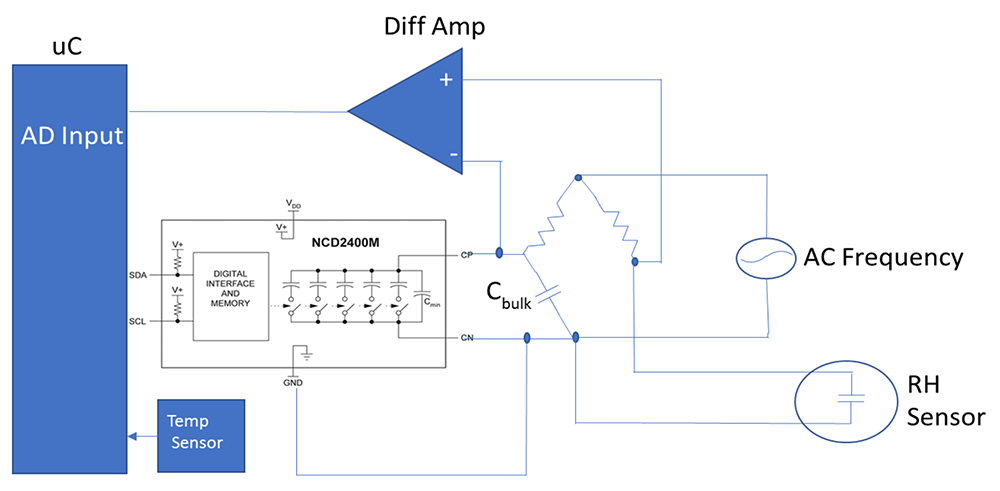

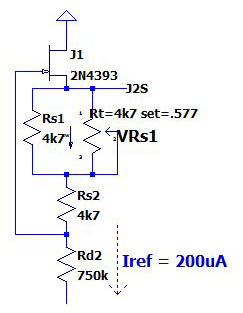

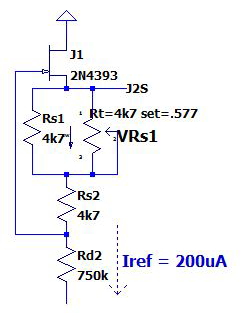

图 3 FET 偏置设置使得启动时 Iref 不会导致 Vce 或 Vds 超过值。 图 4反转 Vout、 ,消除偏移,将输出调整至所需范围,并可过滤输出以处理电源纹波或负载尖峰。如果使用带 ADC 的

微控制器,则电路可简化为仅反转 Vout。

图 4反转 Vout? 可消除偏移,将输出缩放到所需范围,并可过滤输出以处理电源纹波或负载尖峰。