555 时基集成电路是一个把模拟电路和数字电路组合而成的混合电路,它将模拟功能与逻辑功能整合在一片独立的集成电路上,极大地拓宽了模拟集成电路的应用范围。555时基集成电路被广泛用于各种各样的计时器、脉冲发生器和振荡器等场合。凭借着模数结合的优势,555时基集成电路可以独立构成多种功能电路,且精度非常高,能够产生的时间延迟和振荡,其外形如图11-36所示。

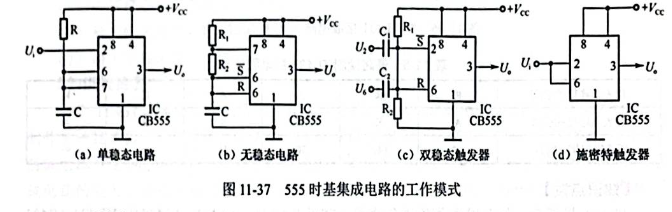

555时基集成电路的工作模式有4个,即单稳态、无稳态、双稳态和施密特模式。图11-37 (a)为单稳态电路,多谐振荡器(无稳态电路)如图 11-37 (b)所示,双稳态触发器如图 11-37 (c)所示,施密特触发器如图 11-37(d)所示。

2. 引脚作用

2. 引脚作用

555 时基集成电路各引脚的作用如下:

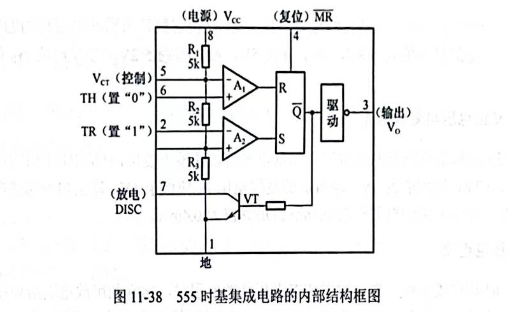

1脚是公共地端为负极: 2脚为低触发端TR,低于1/3电源电压以下时即导通: 3脚是输出端 Vo,电流可达 200mA; 4 脚是强制复位端 MR,不用时可与电源正极相连或悬空;5脚是用来调节比较器的基准电压,简称控制端Vcr,不用时可悬空,或通过0.01uF电容器接地: 6脚为高触发端TH,也称阈值端,高于2/3电源电压以上时即截止; 7脚是放电端DISC; 8脚是电源正极Vcc.

3.内部结构框图

555时基集成电路是一种能产生时间基准并能完成各种定时、延迟功能的非线性模拟集成电路,其内部结构框图如图11—38所示。它广泛应用于信号产生、波形处理、定时延时等领域。

由图 11—38 可看出, 555 时基集成电路将模拟电路与数字电路巧妙地结合在一起,图中1、A2为两个电压比较器,它们的输出分别作为RS触发器的输入信号,输出驱动级和放管VT受RS触发器控制。内部3个分压电阻Ri、 R2、R3的阻值均为5k2,便称为555十基集成电路。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。