I2C 是一种同步、多主、多从串行接口,允许微芯片相互通信。作为一种漏极开路/集电极开路通信标准,I2C 允许

集成电路 (IC) 即使在使用不同的电压轨时也能进行通信。

I2C 标准的四种速度

I2C 标准中有四种运行速度:

标准模式:100kHz

快速模式:400 kHz

快速模式加:1 MHz

高速模式:3.4 MHz

I2C 总线:串行数据和串行时钟

I2C 总线使用两条线——串行数据 (SDA) 和串行时钟 (SCL)——所有 I2C 主设备和从设备仅通过这两条线连接。每个设备既可以是发送器,也可以是接收器。

SDA 和SCL 信号都是双向的。每个器件的 SDA 和 SCL 引脚都是漏极开路引脚。它们连接有上拉电阻以获得逻辑1。逻辑1取决于

电源电压;没有标准总线电压。

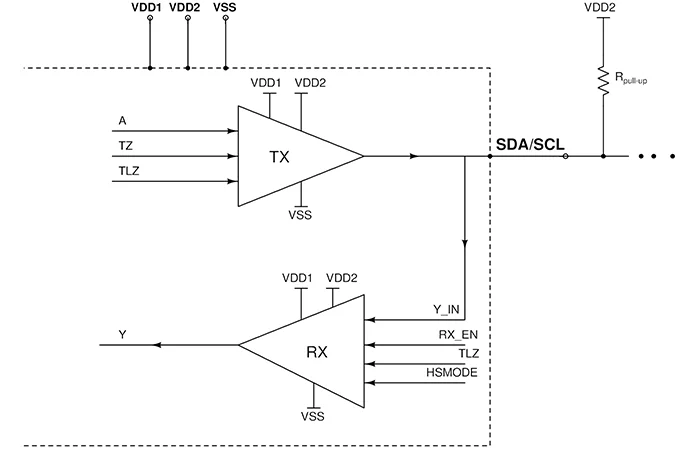

I2C 单元结构

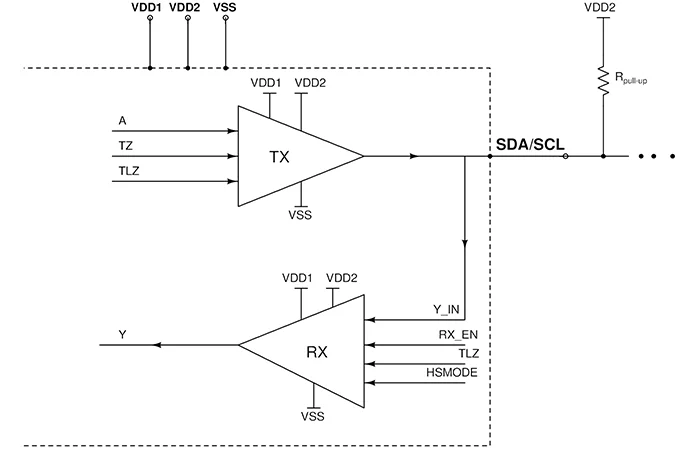

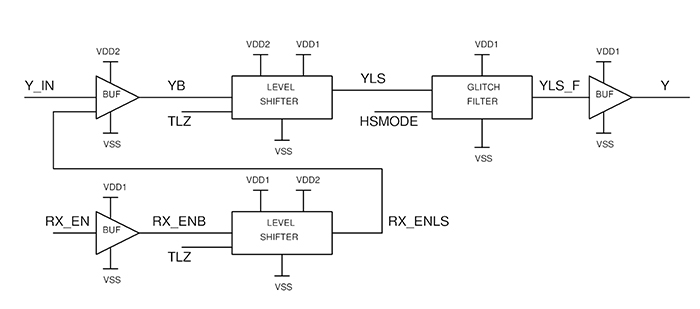

让我们讨论一下 IC 中集成的 I2C I/O 单元结构。I2C I/O 单元结构框图如图 1 所示。

图 1. I2C I/O

驱动器框图

TX 块在发送时间帧中启用,而 RX 块在接收时间帧中启用。

VDD1 和 VDD2 是主设备和从设备工作的两个不同电压轨。VDD1 是芯片内部操作的电源,VDD2 是外部系统使用的电源电压。为了支持不同的电压轨,需要一个电平

转换器将信号从一种电源电压转换为另一种电源电压。

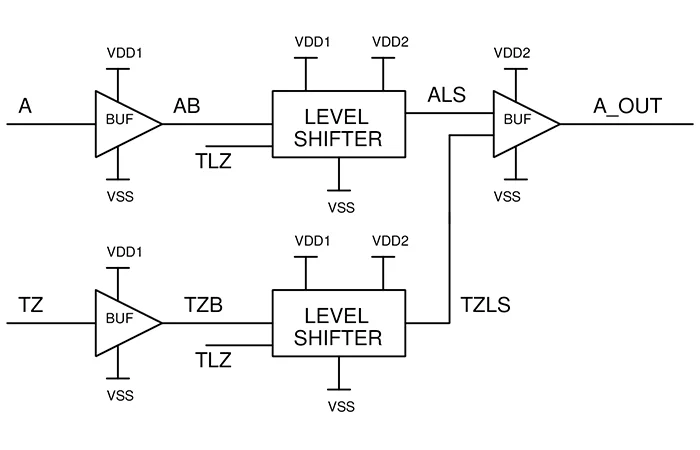

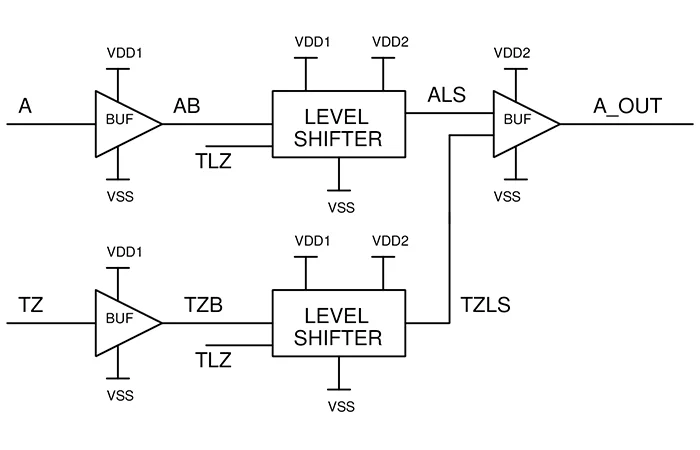

发射机电路框图如图2所示。

发射机框图

图 2.发送器框图

A 是在 SDA/SCL 引脚上发送的数据信号。TLZ 是 VDD1 掉电期间的三态控制。TZ 从 VDD1 电平转换至 VDD2,以启用 A_OUT 的输出开漏缓冲器。

如果 VDD1 在系统运行期间有意或无意地断电,而 VDD2 仍然有效,则 TZ 使能信号变低或大部分处于不确定状态。这可以使能输出缓冲器到A_OUT。

TLZ 信号用作故障安全机制。TLZ 在断电期间被拉低,从而将 TZ 信号拉高。此时,输出缓冲区不再启用。当 VDD1 掉电时,开漏缓冲器将处于三态状态。

要了解有关使用 I2C 缓冲区的用例、优点和应用的更多信息,请查看 AAC 关于何时使用 I2C 缓冲区的技术文章。

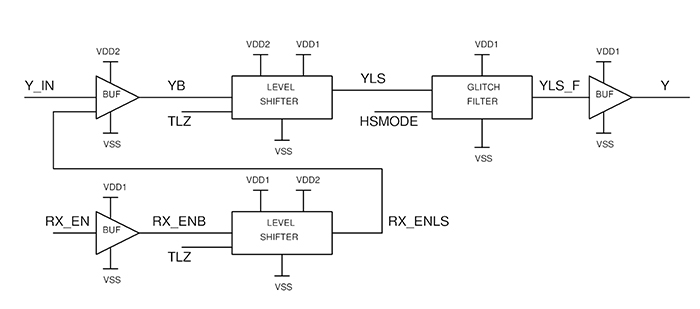

接收器框图

图 3.接收器框图

接收器电路由 RX_EN 信号启用。TLZ 具有与发送器块中相同的功能。HSMODE 信号启用高速模式。

RX_EN 信号从 VDD1 电平转换为 VDD2,以启用接收 Y_IN 信号的缓冲器。然后,电平移位器将缓冲的 Y_IN 信号移位至 VDD1 电压轨。

使用毛刺

滤波器 I2C 信号容易受到噪声和干扰。因此,您需要一个毛刺滤波器来滤除所有不需要的毛刺并只允许有效信号通过。在标准/快速模式下,<= 50ns 的毛刺被抑制。在高速模式下,<= 10ns 的毛刺受到抑制。

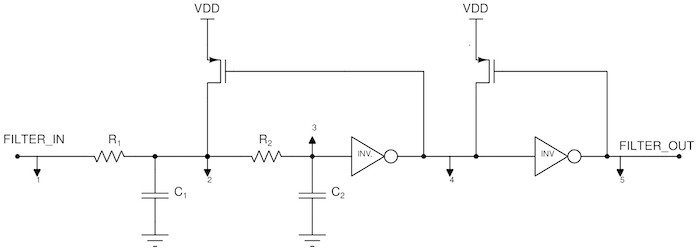

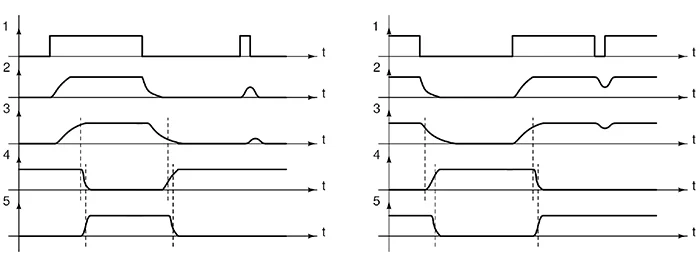

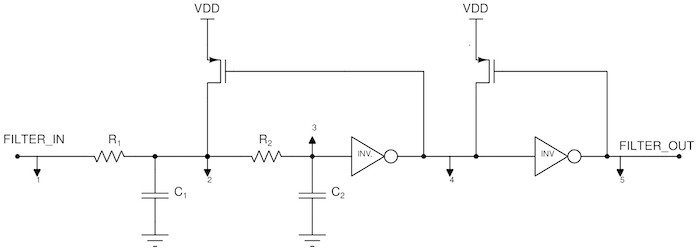

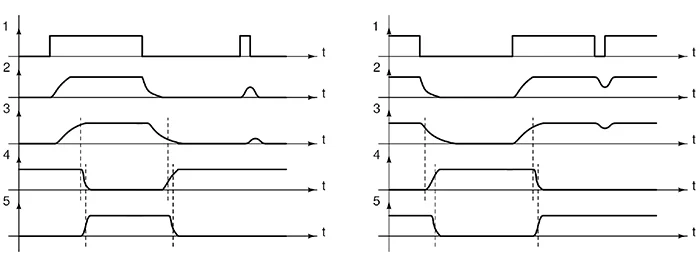

毛刺滤波器设计如图 4 所示,时序图如图 5 所示。 图 4.毛刺滤波器设计

毛刺滤波器时序图

图 5.毛刺滤波器时序图

RC 时间常数延迟传递信号并抑制任何毛刺。R1、C1、R2、C2 组合决定了要抑制的毛刺脉冲宽度。根据 I2C 规范,接收器应能够在标准和快速模式下抑制 <= 50ns 的毛刺脉冲,在高速模式下抑制 <= 10ns 的毛刺脉冲。

毛刺滤波器的输出信号经过缓冲并由 IC 进行处理以供进一步操作。

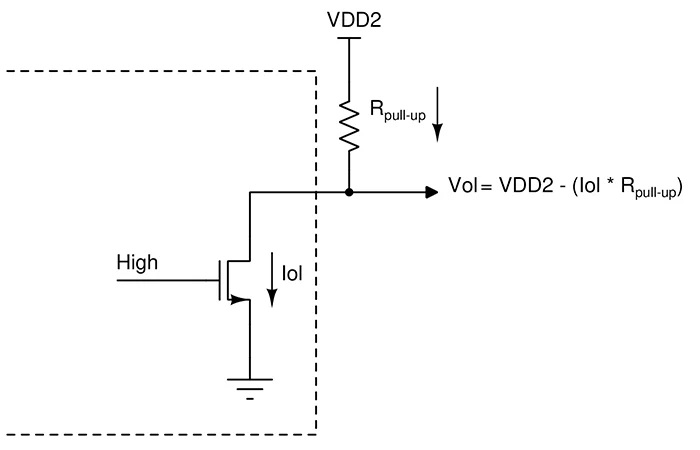

开漏配置中的上拉电阻

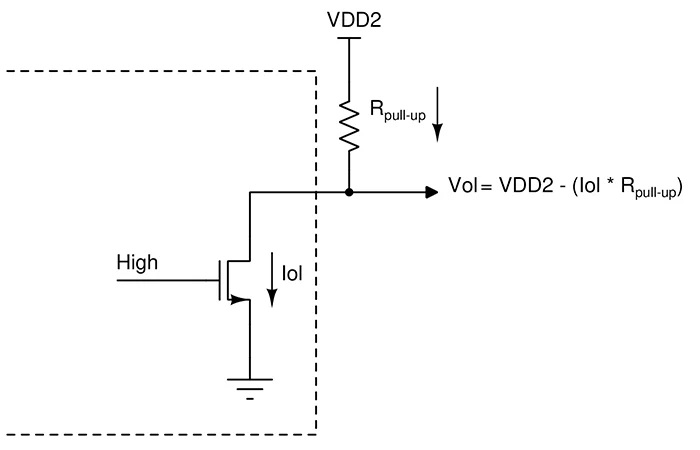

I2C 线路上的输出缓冲器采用开漏配置,我们将在有关 I2C 总线所需硬件的文章中进一步详细讨论这一点。任何 I2C 设备只能将这些 I2C 线路驱动为低电平或将它们置于三态。为了获得逻辑高电平,需要上拉电阻在三态条件下将它们拉至电压轨。

当器件驱动为低电平时,这些上拉电阻通过 NMOS 汲取电流,如图 6 所示。

图 6.开漏配置

上升时间取决于上拉电阻和寄生电容时间常数,并且通常比下降时间长,因为下降是由器件(即NMOS)驱动的。因此,不同的操作速度需要不同的上拉电阻。

有关上拉电阻和电容负载的更多信息,请查看我们关于电容和电阻的 I2C 数学的文章。