本文档描述了信号完整性、传输线行为的基础知识,并比较了各种逻辑器件的输出边沿速率。它还解释了传输线上反射的原因,并提出了避免反射的有效端接方案。,本文还提供了恩智浦产品组合中带有集成源端接电阻的逻辑器件示例,以实现更好的系统信号完整性。

简介:什么是信号完整性?

在具有高速相互通信的 IC 的

电子系统中,信号完整性是确保系统可靠性的重要组成部分。决定信号完整性的关键因素是信号的时序和质量。重要的是,以“1”或“0”形式发送的数字信号在所需时间被接收为“1”或“0”,以便可以正确采样和检测。反射噪声通常是由阻抗失配、短截线、通孔或其他互连不连续性造成的。

输出边缘速率比较

影响信号完整性的重要参数包括传播延迟、上升和下降时间以及系统数字逻辑器件及其模拟

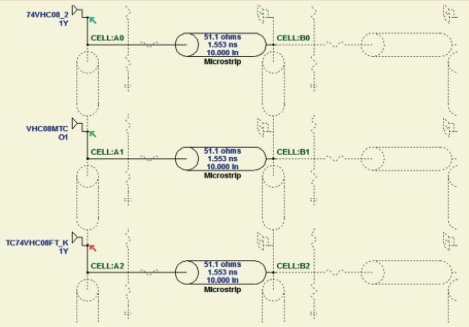

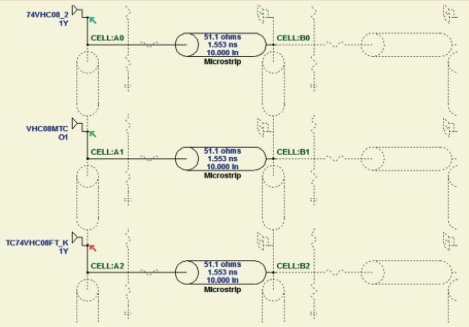

开关的输入阈值电压。图 1 显示了

NXP、

Fairchild 和 Toshiba 驱动开放式无端接传输线的 74VHC08 器件的 IBIS 模型。

图1 74VHC08驱动无端接传输线的IBIS模型

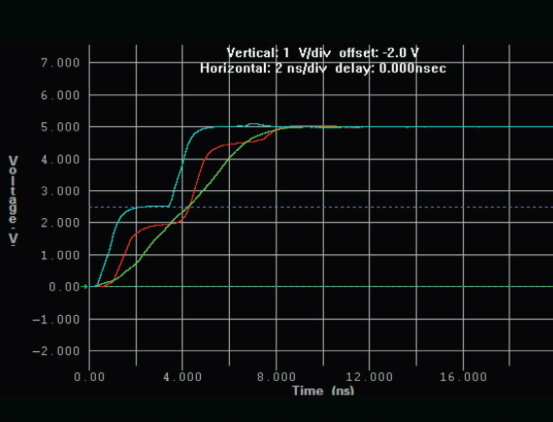

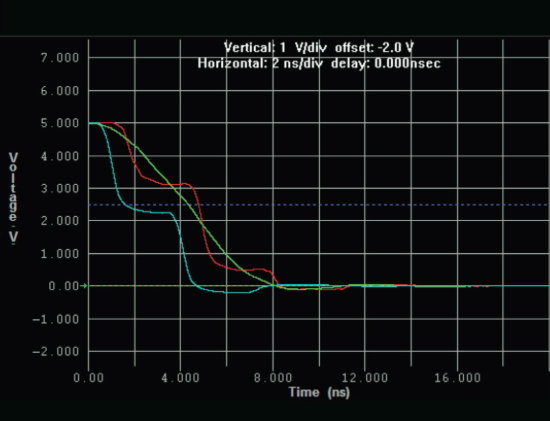

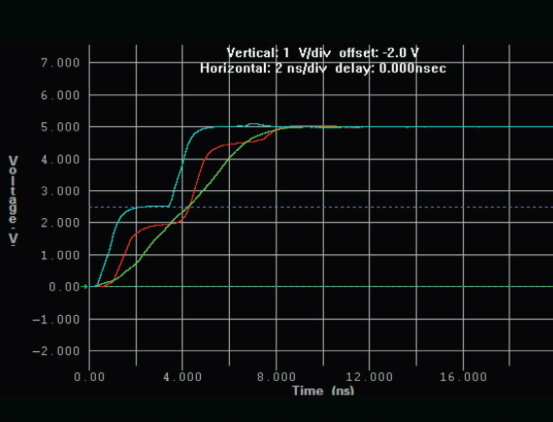

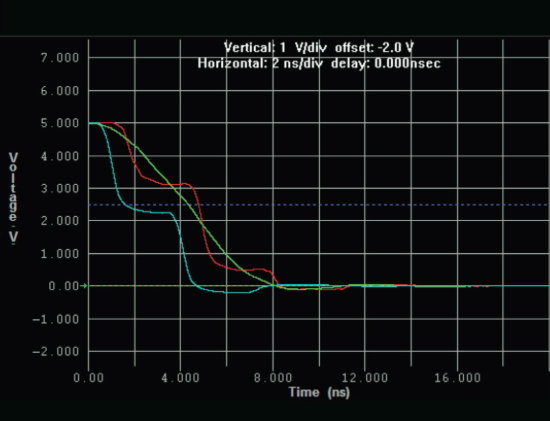

上升沿和下降沿的输出波形如下图 2 和图 3 所示。表 1 和表 2 显示了相应转换速率的上升时间和下降时间。

图 2 图 1 电路的输出上升沿波形。

图 2 图 1 电路的输出下降沿波形。

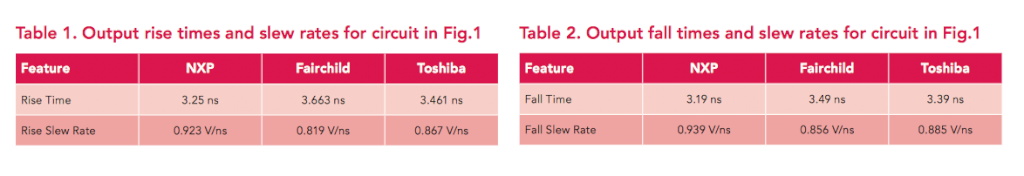

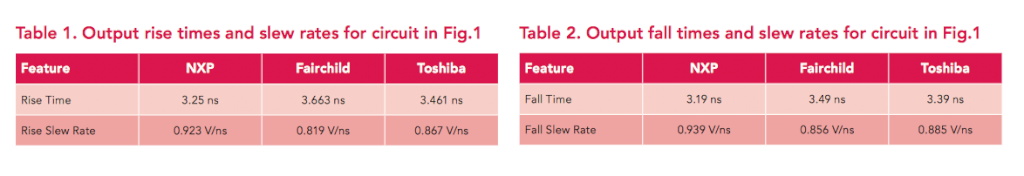

表1和表2

可以看出,NXP 的 VHC 逻辑的输出沿比 Fairchild 和 Toshiba 的 VHC 逻辑的输出沿更快。通常,NXP 的 VHC 逻辑的输出上升沿 Fairchild 的 VHC 逻辑的输出上升沿 0.41 ns,东芝的 VHC 逻辑的输出上升沿 0.21 ns。而且,NXP VHC 逻辑的下降输出沿通常 Fairchild VHC 逻辑的下降输出沿 0.3 ns,东芝 VHC 逻辑 0.20 ns。因此,这些竞争对手的 VHC 逻辑可以在系统中替换为 NXP 的 VHC 逻辑,该逻辑具有如上所述,有足够的时序余量。

图1 74VHC08驱动无端接传输线的IBIS模型

图1 74VHC08驱动无端接传输线的IBIS模型 图 2 图 1 电路的输出上升沿波形。

图 2 图 1 电路的输出上升沿波形。 图 2 图 1 电路的输出下降沿波形。

图 2 图 1 电路的输出下降沿波形。 表1和表2

表1和表2