在生成干净或可靠的复位信号之前,监控器 IC 所需要的只是称为上电复位 (VPOR) 的电压。在达到电源电压之前,复位信号的状态是不确定的。

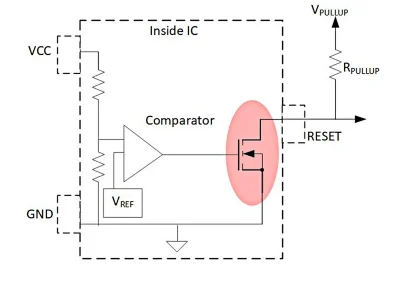

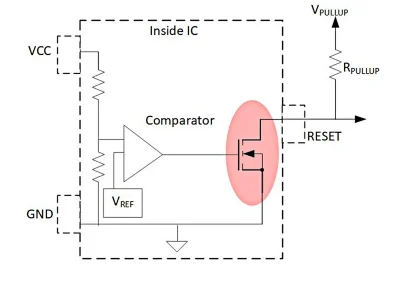

漏极开路配置

推挽式配置

图 1. 用于复位拓扑的开漏配置和推挽配置。图片由 Bodo's Power Systems提供

一般来说,我们称这种故障为复位。RESET 引脚主要使用两种不同的拓扑:漏极开路和推挽式(图 1)。两种拓扑均使用 NMOS 作为下拉

MOSFET。

上电期间,如果电源电压低于V POR,则内部电路没有足够的电压驱动输出MOSFET 工作,因此输出MOSFET 关闭。监控器无法控制输出复位电压。复位电压将与上拉电压 (V PULLUP ) 成比例上升,一旦电源电压高于 V POR电压,内部 MOSFET 将驱动 RESET 引脚至有效状态。

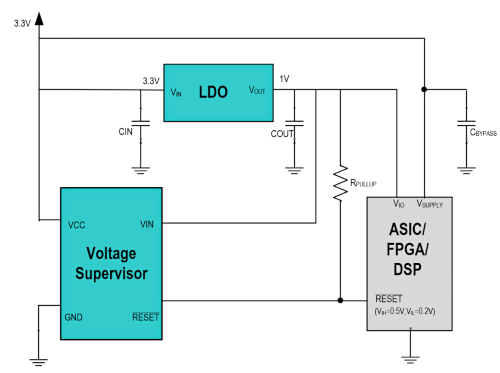

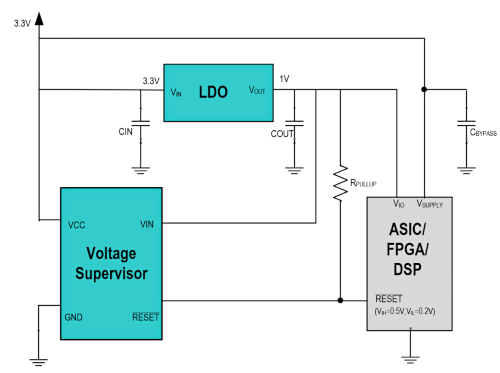

电压监控器可用于监控 FPGA、ASIC 或 DSP 的低压轨,其中电压可低至 1V。在低电压处理器中,I/O 逻辑电平非常敏感,VIH 可以低至 0.5V,如图 3 所示。

上电期间,FPGA、ASIC 或 DSP 需要处于 RESET 状态,直到所有电源轨稳定为止。由于当 VDD 低于 V POR时, RESET 可能会出现故障,因此该故障可能会触发 FPGA 的未知状态。一旦 VDD 高于 V POR电压,内部 MOSFET 就会导通,将 RESET 连接到 GND,并使 RESET 输出正确的低逻辑电平。

范围象征状况典型值限度单位

输入电压

输入电压范围电压CC工作范围1.7 5.5 复位输出保证处于已知状态1.5 V

图 2. 这就是复位如何与上拉电压 (VPULLUP) 成比例上升,从而导致通常所说的复位毛刺。图片由 Bodo's Power Systems提供

图 3. 监控器与低压 ASIC、FPGA 或 DSP 的接口。图片由 Bodo's Power Systems提供

图 4. 复位时出现故障的上电顺序。图片由 Bodo's Power Systems提供

随着

电子行业向低压半导体发展,模拟芯片制造商也在努力提供传统监控器的无故障监控器。制造商只能通过改进工艺来降低 V POR电压,但真正的无故障监控器需要新的架构。 目前,系统工程师使用带有传统监控器的外部电路来模拟图 5 所示监控器的无毛刺特性。通过添加配置为源极跟随器配置的标准 JFET,源极电压将跟随VG 减去 JFET 的阈值电压。JFET 的阈值导致 VG 和 VOUT 之间出现大约 1V 的压降,并消除输出上的电压电位上升,直到内部电路开始运行。

图 5. 具有外部 P-JFEF 的传统监控器,可实现无故障运行。图片由 Bodo's Power Systems提供

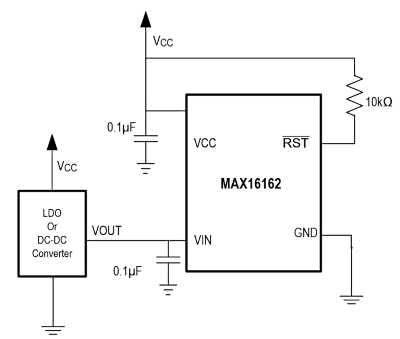

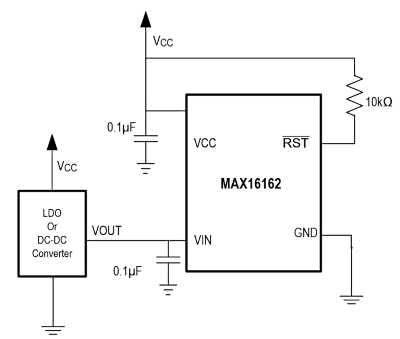

图6. MAX16162的应用图和相应的时序图。图片由 Bodo's Power Systems提供

真正的无故障监控器可以通过复位吸收电流,即使在 VCC 为零的情况下,也会强制复位至接地电位。图 6 显示了电路中真正无干扰监控器的示例。MAX16161/MAX16162无需任何外部元件即可实现无故障运行,因此尺寸小巧且具有成本效益。