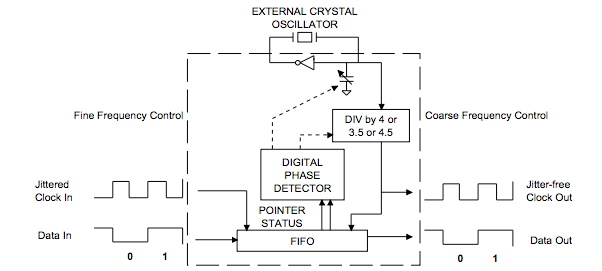

图 1 显示了衰减器电路。抖动衰减器减少恢复时钟信号中的抖动。它由 FIFO、晶体振荡器、一组晶体负载电容器和控制逻辑组成。恢复的时钟和数据被输入到 FIFO,恢复的时钟控制 FIFO 的写指针。晶体振荡器控制 FIFO 的读指针,该指针从 FIFO 中读取数据。通过改变 IC 提供给晶体的负载电容,振荡频率可以精细调整到恢复信号的平均频率。逻辑决定了读写指针之间的相位关系,并决定如何调整晶振的负载电容。因此,抖动衰减器的作用相当于一阶锁相环。信号抖动被 FIFO 吸收。

抖动衰减器中的 FIFO 设计为既不会溢出也不会下溢。如果抖动幅度变得非常大,则读写指针可能会非常接近。如果它们试图交叉,振荡器的四分频电路会通过执行除以 3.5 或除以 4.5 进行调整,以防止 FIFO 上溢或下溢。这是对输出时钟的粗调。在此活动期间,数据永远不会丢失,但会出现抖动增益。

衰减器设计的性能影响

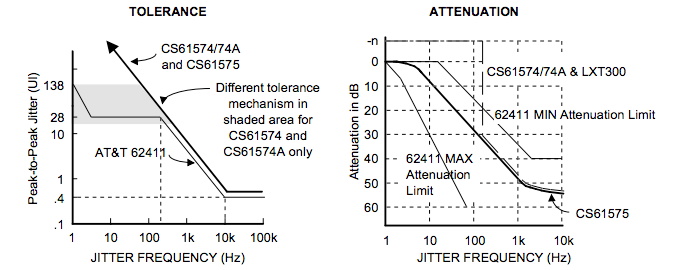

AT&T 62411 要求的变更

1990年12月,AT&T改变了62411使用的高频抖动传输测试程序,正式要求60 dB的衰减(任何供应商的任何线路接口IC在所有操作条件下都无法达到该性能水平),的62411规范仅要求40 dB的衰减。免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。