可靠性是系统在一定时间内继续正确运行的保证。在本文中,我们将讨论 MOS(金属氧化物半导体)非理想性作为 VLSI(超大规模集成)系统中的故障机制,以及它们如何影响系统可靠性。

0.25

氧化物磨损

正如在上一篇关于VLSI 电路中的非理想性的文章中所讨论的,在难以置信的小晶体管中,栅极氧化物可能只有几个原子那么厚。虽然这可以使设备小型化,但它也会由于电流隧道效应而导致泄漏。

此外,随着设备老化,这种非理想性会变得更糟,因为氧化物会磨损。结果,阈值电压发生偏移,进一步增加了栅极泄漏。这种效应的一个更重要的影响是晶体管失配或高漏电流会导致电路故障。

氧化物磨损的三个主要原因是:

热载体

负偏压温度不稳定性 (NBTI)

随时间变化的电介质击穿 (TDDB)

热载体

在快速 VLSI 电路中,晶体管每秒开关数百万次。在开关过程中,被称为“热载流子”的高能载流子(电子或空穴)很容易注入并被捕获在栅极氧化物中。这种热载流子注入会在栅极氧化物中产生杂质,从而改变器件的 I-V 特性。

这种注入会导致几个问题。它使 NMOS 晶体管运行更慢,导致电路失配。它还会在 PMOS 晶体管中引起高电流浪涌,从而导致严重的电路故障。

为了模拟或建模 VLSI 电路中的热载流子,Hsu 等人提出了一种分析方法。al(1991 和 1992)和 Quader 等。阿尔。

负偏压温度不稳定性 (NBTI)

NBTI 会导致 p 沟道 MOS 晶体管的阈值电压增加、迁移率下降、漏极电流和跨导。NGTI 发生在高温下硅/氧化硅界面存在陷阱的情况下。

由于高温下的强负偏压(栅极电压为 0 和源极电压为 V DD ) ,这种效应在 PMOS 晶体管中更为突出。NBTI 的主要作用是导致迁移率降低和阈值电压升高,从而导致数字电路延迟增加。

根据 Alam 和 Mahapatra 的说法;杰普森和斯文森;还有小川和盐野;可以使用反应扩散 (RD) 模型对 NBTI 进行建模。保罗等。al 还建议阈值电压偏移可以建模为

ΔVt=keEoxE0t

时间相关的介电击穿 (TDDB)

TDDB 是指存储在低于材料击穿强度的恒定电场下的电介质随时间分解的物理过程。

在 MOS 晶体管中,栅极氧化物是电介质;当在栅极氧化物上施加电场时,电流将逐渐增加。当电场施加一定时间后,会导致严重的电介质击穿,从而使栅极短路。

已经针对 TDDB 的电场依赖性提出了两个主要模型:阳极空穴注入 (AHI) 模型和 E ox模型。Moonen 等人对这些模型进行了修订研究。

电迁移

电迁移经常发生在承载单向电流 (DC) 的导线中。在运行期间,互连通常会经历“电子风”,因为高电流密度会导致金属原子随时间迁移。它通常可以通过检查空隙的形成来观察 (Hu et. al)。

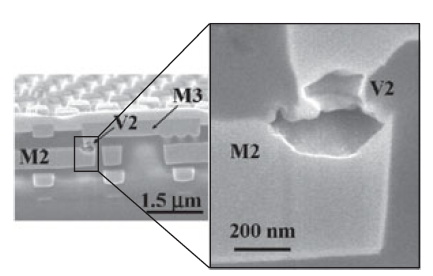

图 1 显示了 M2 和 M3 层之间的通孔电迁移失败的显微照片(Christiansen 等人)。

图 1. M2-M3 的电迁移失败。图片由 Christiansen 等人提供。阿尔

空隙的存在会增加互连的电阻,而小丘的存在会导致不同层次互连之间的短路(Jaikaran et. al)。

由于电迁移取决于电流密度,J. Black 提出了一个模型,用于计算给定平均无故障时间 (MTTF) 和工作温度 T 下直流密度 J dc给出的允许电流。

MTTF∝eEakTJndc

其中 E a是活化能

闩锁

闩锁是一种发生在 CMOS 芯片中的短路。CMOS 在 V DD和 GND之间形成低电阻路径的趋势会导致严重熔化并增加 IC 的故障率。理论上,闩锁发生在由衬底、阱和扩散形成的寄生双极晶体管导通时。

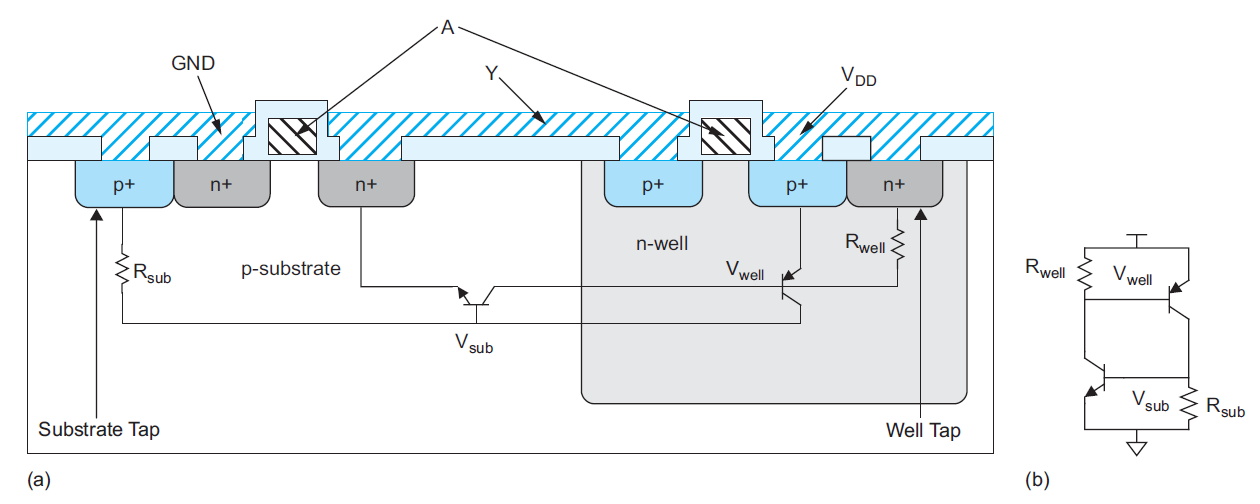

图 2 显示了在 CMOS 反相器中形成的 BJT 对的等效电路。

图 2. CMOS 闩锁模型

除了 NMOS 和 PMOS 晶体管之外,该电路还包含一个 PNP 和一个 NPN 晶体管,连接到两个电阻器,这两个电阻器连接在电源和接地轨之间。电阻器是由于附近的基板和井抽头之间的电阻。

通常,BJT 晶体管处于关闭状态。但是当电流流过基板 (R sub ) 时,V sub将上升,这将打开 NPN 晶体管。结果,NPN 晶体管通过 R well拉动电流,从而导通 PNP 晶体管。

PNP 晶体管还将通过 Rsub 拉动电流,从而提高Vsub。这个周期形成了一个正反馈回路,导致大电流在 V DD和 GND之间来回流动。如果这个循环持续很长时间,它会产生热量并熔化电源轨。

幸运的是,可以通过降低衬底和阱之间的电阻来防止闭锁。实现这一点的常用方法是将衬底和井抽头放置在靠近每个晶体管的位置(Neil 和 David)。

在某些应用中,如图 3 所示的保护环适合包围晶体管并在晶体管和电源轨之间提供低电阻路径。

图 3.保护环

结论

到目前为止,我们已经讨论了 MOS 晶体管的非理想特性以及它们如何影响 VLSI 系统的可靠性。关于如何衡量和模拟它们对设计的影响,已经讨论了几种模型。

幸运的是,现代 SPICE 模型和 CAD 工具在预测千兆赫兹范围内各种设计的性能方面是全面而准确的,同时考虑了这些非理想因素的影响。利用这些工具可以推动芯片开发生命周期中的自动化和更快的设计时间。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。