的数字设备设计得越来越小、越来越快,效率也更高。主流 5V 逻辑电平被越来越低的 3.3V、2.5V、1.8V 甚至更低的电压标准所取代,因此需要一种方法让不匹配的系统能够可靠、有效地进行通信。设计者需要确保逻辑 1 或逻辑 0 可以在这些平台上以一种可预测的方式实现。

二进制或两级逻辑电压之间的转换/隔离促进了可预测的电路行为。设计者可能会认为 3.3 V 的信号在 5 V 引脚上“应该有效”,但并不是在所有条件下总是如此。相反,在大多数情况下,在一个接受 3.3V、5 V 电压的引脚上使用 5V 信号肯定是有效的,但这种方法由于需要额外的元件且在某些情况下要“烧掉”多余的电压,所以成本更高。

有替代方案吗?

有源转换器/电平位移器件解决了常见的转换问题,甚至可能提供额外的有用功能,如反相、推挽输出、三态或差分功能。但是,如果有不太复杂的东西允许实现更宽的逻辑电压水平和双向通信那怎么样?一个分立、紧凑的 MOSFET 可以以高频率和高效率完成转换。使用这些廉价的半导体和一些额外的无源器件,可以对像 I2C 和直接 GPIO 引脚到引脚连接这样的通信方式实现电平位移。适当地选择 MOSFET 就可以实现更高的逻辑电压,例如 12 V 或 18 V 也可用于监测汽车电路就是一例。

注意:采用 Hs 模式(高速模式)的 I2C 可能需要更精细的元件,如 NXP 的 PCA9306 双向转换器。

实例: BS170 (N 沟道增强模式场效应晶体管)

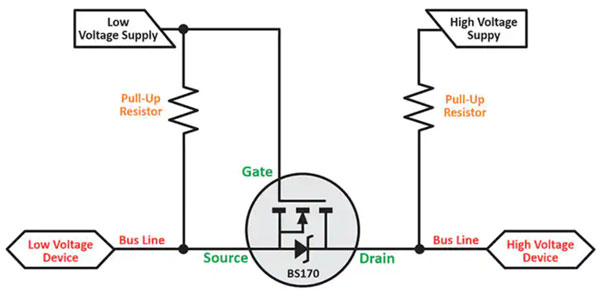

BS170 旨在限度地减少导通电阻,同时提供可靠和快速的开关性能,适合低电压、低电流开关应用。图 1 显示了进行基本通信或 GPIO 逻辑电平位移所需的连接。

图 1:基本、单总线、电平转换 MOSFET 电路。

MOSFET 两侧的逻辑高电平是通过上拉电阻实现的,其各自的电源提供快速模式 (400 kHz) I2C 信号或其他类似的快速数字接口的转换。MOSFET 的栅极被保持在低压供电水平。当没有器件拉低总线线路电压时,MOSFET 的源极的总线线路就会被低压上拉电阻拉高。MOSFET 的栅/源电压 (VGS) 低于阈值,MOSFET 不导通。这使得 MOSFET 漏极的总线电压被高压上拉电阻拉起。MOSFET 两侧的总线保持为高电平,但处于不同的电压水平。见图 2。

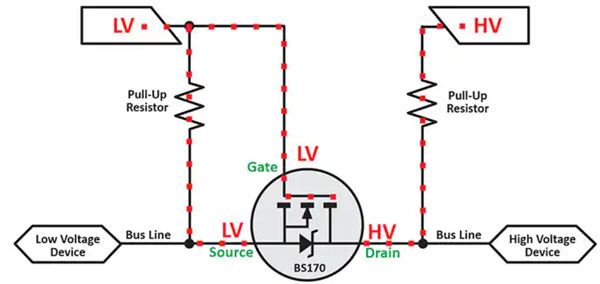

图 2:逻辑高电压转换。

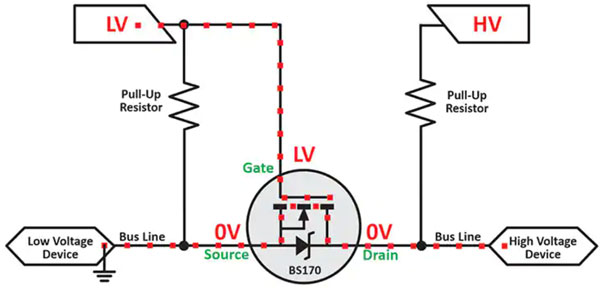

如果低压器件拉低 MOSFET 源极的总线电压,而栅极保持在低压供电水平,则 VGS 会上升到阈值以上,然后 MOSFET 开始导通。此时 MOSFET 漏极的总线电压也会被拉低。参见图 3。

图3:由低压器件启动的逻辑低电压转换。

如果高压器件拉低了 MOSFET 漏极的总线电压,MOSFET 的基底二极管允许源极也被部分拉低,这是因为二极管上有少量的电压下降。见图 4。

图 4:由高电压器件启动的近逻辑低电压转换。

当 MOSFET 的源极被部分拉低时,VGS 上升到阈值以上,MOSFET 开始有效地绕过基底二极管进行导通。见图 5。

图 5:由高电压器件启动的全逻辑 LOW 电压转换。

这三种状态显示了在总线系统的两个方向上转换的逻辑电平,与驱动部分无关。根据 MOSFET 的能力,实现多组合高电压和低电压供电是可能的。无论逻辑电平冲突是涉及点对点 GPIO、传感器输出还是双向多线路通信,MOSFET 电平移位器都是有用的工具。图 5 展示了一个使用两个 MOSFET 实现的转换后、双线、双向通信电路。

图 6:双线双向转换数据通信电路。

隔离

为了防止在高压设备断电或高压电源断电的情况下出现随机的逻辑电平,可以采用额外的 MOSFET“漏极到漏极”来隔离高压逻辑总线线路。

图 7:转换后的数据通信电路中的隔离总线线路。

开发板

为了详细了解逻辑电平转换,一些制造商生产了开发板,装有 MOSFET 或逻辑转换器件以及所需的外围无源器件,以便进行快速连接和实验。

结语

选择合适的 MOSFET 和上拉电阻是这种简单而有效的逻辑转换方法的成功关键。典型器件数据手册中包含了实验所需的信息。在大多数情况下,BS170 的上拉电阻在 4.7 Khm 到 10 Khm 范围内可能效果很好。专用逻辑电平转换器 IC 也可以提供额外的功能,如 I/O 和供电电压输入的 15kV ESD 保护。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。