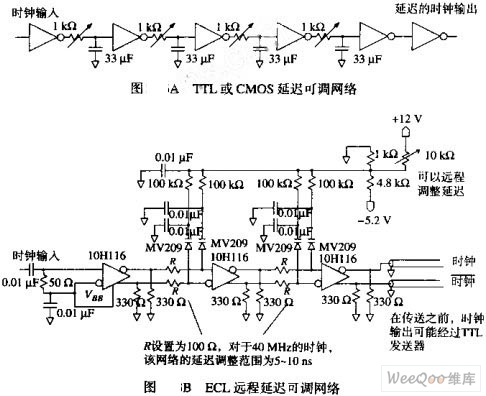

图A所示的电路,是一个16进制的反相器,用于产生30~160NS的延迟。每的延迟时间是5~35NS,具体数值由可变电阻的值决定。每的延迟时间不应该超过时钟周期的12%,以保重稳定工作。

通过调整延迟级数(2或4)并平均地调整每级电路的电阻(用排电阻),可以调整电路的占空比,使之到达一个值。在信号重新进入到系统之前,在电路的末端至少用一个反相器来对信号进行整形。

图A所示电路的缺点是信号必须经过电位器。对于调整系统,这意味着电位器必须非常小,并且在物理位置上离电路很近。图B所示的电路通过使用变容二极管的方法,解决了这个问题。变容二极管指的是其电容会随着偏置电压的变化而变化。图B所示电路的工作频率远远高于图A所示的电路。

图B所示电路的每电路延迟时间都在2.5~5NS之间。该电路通过变容二极管MV209组成RC网络来调整相移。电路的级联使得延迟时间的可调范围扩大。图B是两级电路,基延迟时间是5~10NS。

这个电路的设计频率是40MHZ,如果工作在其他频率,可以重新选择R值:

为保征更高的稳定性,应该给这个可变延迟电路提供独立的稳压电源,并使电源的温度保持恒定。

采用两个电路中的任何一个,两路信号都应取自同一个时钟源,其中一路信号(时钟A)通过可调延迟网络,另一路信号(时钟B)通过固定长度的同轴电缆直接连接到总线。所用同轴电缆的阻抗要与总线原来的阻抗匹配。选择同轴电缆的长度,使得可调延迟调整到中间值时,输出的两路时钟信号的时序相匹配。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。