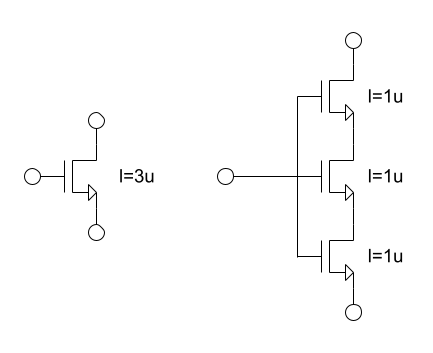

这些串联器件通常称为堆叠式

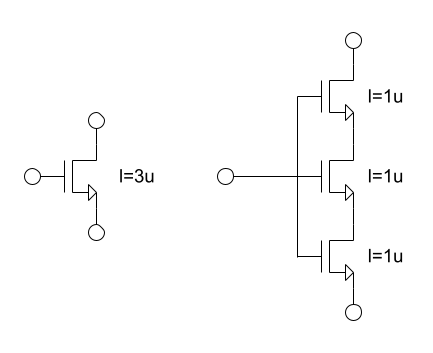

MOSFET 或堆叠式器件。例如,将三个 1 um

MOSFET 串联起来,可以产生一个通道长度为 3 um 的有效器件(图 1)。

关于模拟布局中的堆叠式 MOSFET 的所有信息

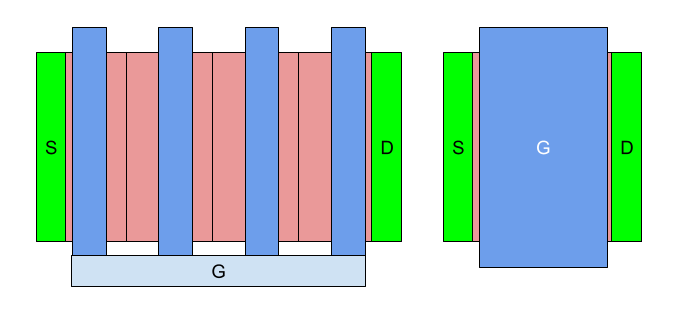

图 1三个 MOSFET 串联堆叠,提供 3 um 的通道长度。Pulsic

堆叠式 MOSFET 在现代模拟设计中非常常见,但并非没有问题。主要问题是电容增加和面积增加。电容的增加主要是由于器件周围互连的增加。整体栅极面积和栅极电容与非堆叠等效电容相似,但互连上有额外的寄生电容。与单个长通道器件相比,堆栈中器件的物理分离增加了整体设计面积。

在电路中使用堆叠式 MOSFET 时,布局质量变得比平时更加重要。不良的布局会显著增加寄生电容和设计面积,并可能导致电路无法满足所需的性能特征。因此,工程师必须非常小心地设计此类设备的布局。在这些较小的工艺节点上工作的大多数设计人员都经历过版图前和版图后仿真非常不同的情况。很多时候,这是由于 interconnect parasitics 对 stacked devices 的影响。

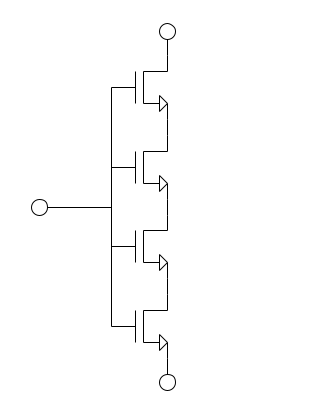

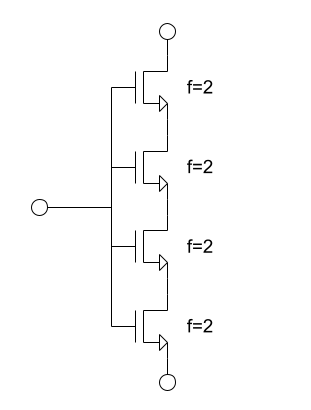

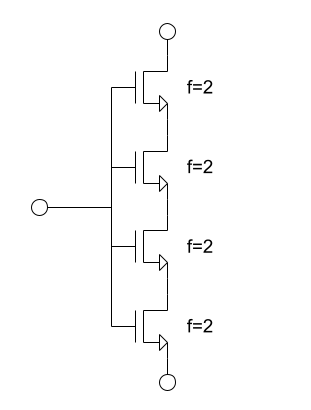

让我们来看看实现堆叠式 MOSFET 高质量布局的几种方法。下面的子电路显示了四个 NMOS MOSFET,它们堆叠在一起以形成一个长通道器件(图 2)。

关于模拟布局中的堆叠式 MOSFET 的所有信息

图 2四个 MOSFET 堆叠在一起,形成一个长通道电路。Pulsic

在这个电路中,您可以看到所有栅极

引脚都已连接(所有四个体连接也是如此),您还可以看到 MOSFET 已串联,一个 MOSFET 的漏极连接到下一个 MOSFET 的源极。因为,在这种情况下,每个器件都是一个简单的单指 MOSFET,所以我们在为这种结构设计布局时可以使用简单的扩散共享布局模式。

关于模拟布局中的堆叠式 MOSFET 的所有信息

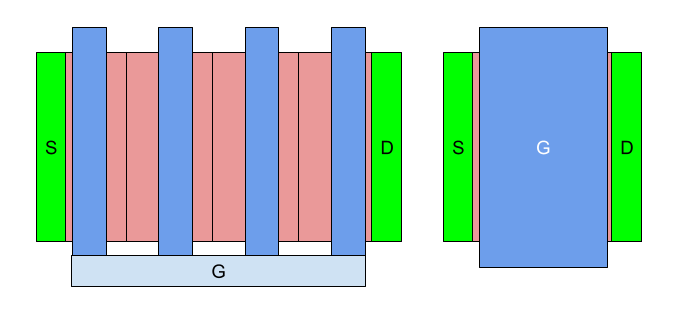

图 3将左侧的简单堆叠

外壳与右侧的等效长通道器件进行比较。Pulsic

简单堆叠箱的布局如上图 3 的左侧所示;您可以看到,额外的互连非常少,因为等效的长通道器件(右侧)也需要一个 Poly

触点。在这种情况下,面积损失很大,但这是不可避免的,并且由 poly min-spacing 规则决定。

这种方法的另一个问题是,非常长的有效设备可能会导致长长的扩散共享链。但是,可以将长链折叠到多行上,如下图 4 所示。权衡是这增加了额外的互连,并进一步增加了堆叠器件的电容。

关于模拟布局中的堆叠式 MOSFET 的所有信息

图 4长链折叠成多行。Pulsic

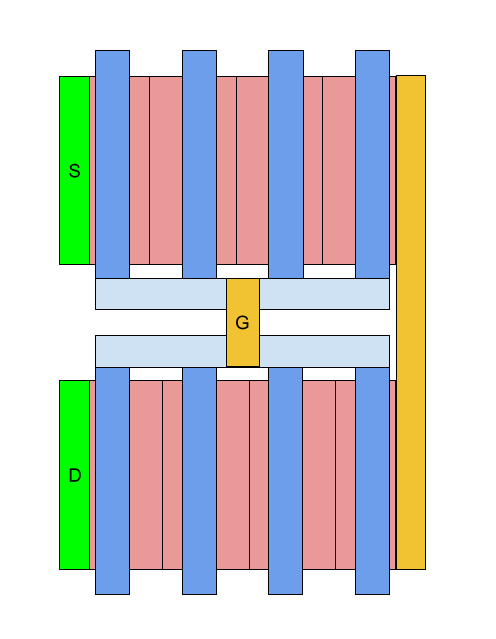

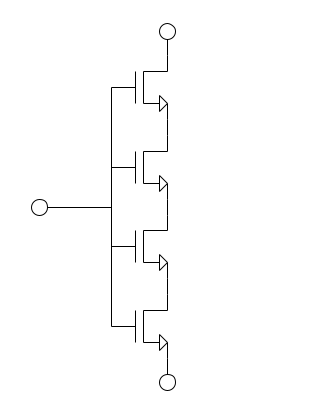

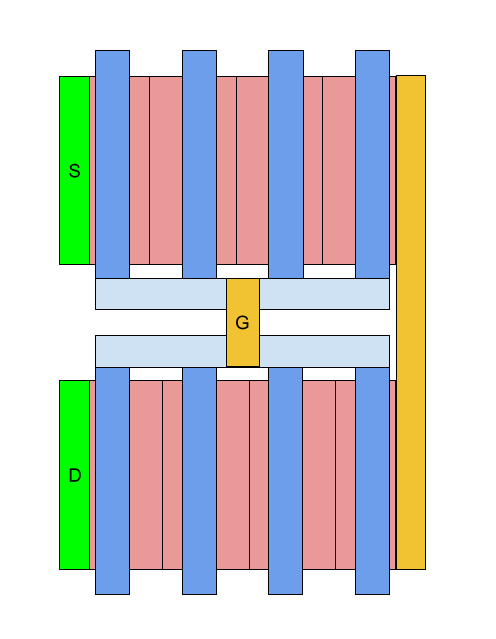

以下电路显示了电路设计人员希望在电路中使用双指 MOSFET 以实现更好匹配的情况(图 5)。

关于模拟布局中的堆叠式 MOSFET 的所有信息

图 5该电路使用双指 MOSFET 来实现更好的匹配。Pulsic

双指器件无法通过扩散共享连接,因此我们必须使用不同的布局和布线方法。为了实现紧凑的布局,设备以列为单位连接,而不是上一个示例中显示的基于行的模式。

关于模拟布局中的堆叠式 MOSFET 的所有信息

图 6连接在列中运行(左),这种基于列的模式的路由机制显示在右侧。Pulsic

在图 6 中,左图显示了连接模式,一个器件的漏极垂直连接到下一个器件的源极。如您所见,连接以列为单位运行,交替的器件具有不同的参数,这些参数在 MOSFET 的漏极中心和源极中心变体之间交换。交换的触点允许在列中的器件之间进行直线布线,避免弯曲和额外的过孔。

您可以在右侧看到这种基于列的模式的路由机制。有额外的互连,但不会明显超过触点加固通常所需的数量。

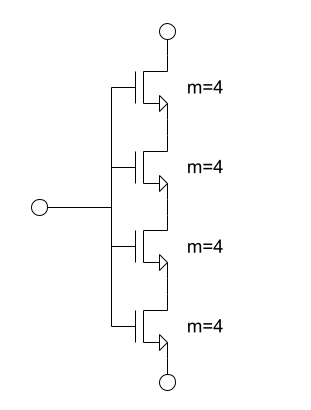

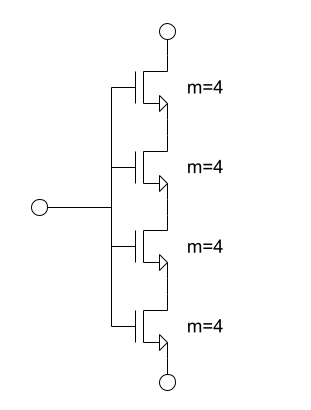

电路设计人员还可以为堆叠器件指定 m 因子。堆叠式和 m 因子拓扑允许电路设计人员使用大量小型 MOSFET 构建具有长通道和宽通道的器件。图 7 显示了一个 m 因子为 4 的单指堆叠器件。

关于模拟布局中的堆叠式 MOSFET 的所有信息

图 7单指堆叠器件采用 m 因子拓扑。Pulsic

该博客展示了一些可用于堆叠式 MOSFET 的基本模式。在所有这些示例中,器件的布局和布线对于实现高质量布局至关重要。