垂直GaN器件面临的挑战之一是其经济可行性,这主要是由于GaN晶圆的高成本。目前,6 英寸 GaN 衬底正在开发中,2 英寸和 4 英寸衬底已投入量产,但晶圆(包括外延层)的成本目前高达 40-60 美元/cm 2 ,而晶圆成本约为 7 美元。 /cm 2对于 4 英寸 SiC 或 ~1$/cm 2对于 8 英寸 GaN-on-Si。尽管与 SiC MOSFET 相比单极 R ON ×A 品质因数在理论上有所改进,但必须降低这一相对较高的价格才能确保垂直 GaN 晶体管的突破。在垂直器件结构中,只有 CAVET 具有与具有相同栅极模块的传统 HEMT 相同的异质结构。虽然不同的外延层被用作垂直耗尽区,但是该工艺技术可以广泛地采用已知的横向器件。 CAVET 的这一独特卖点开辟了一种将垂直器件概念中的横向 GaN 功率集成继续集成到垂直 GaN 功率 IC 的方法(图 1),并且可能成为未来有前途的垂直结构。

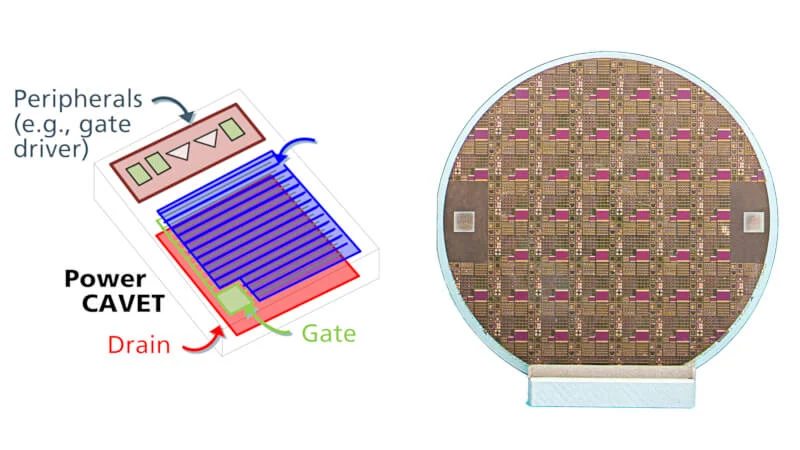

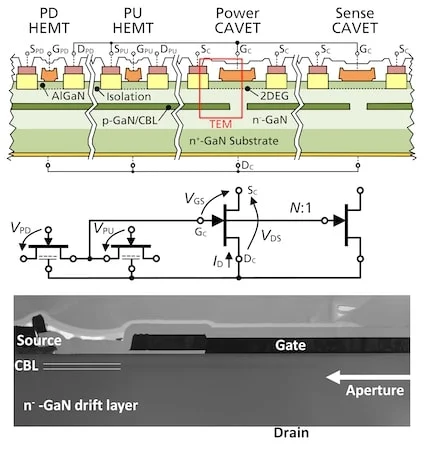

Fraunhofer IAF开发了一种技术,将大面积垂直GaN功率晶体管与横向器件相结合,在单芯片上实现外围功能。 CAVET 将众所周知的横向 HEMT 栅极模块与垂直耗尽区和漂移区相结合。因此,用于 HEMT 的相同常关概念(例如,pGaN 栅极)可以应用于 CAVET。该技术从高负掺杂 (n + ) GaN 衬底和随后的同质外延开始,与硅或蓝宝石等异质衬底上的异质外延相比,其位错密度明显更好,因此可以对击穿电压和可靠性产生积极影响。借助 MOCVD(金属有机化学气相沉积),在顶部生长出几微米的较弱 n 掺杂 (n- ) GaN 层,作为耗尽区和漂移区。然后通过镁注入制造正掺杂 (p) GaN 电流阻挡层 (CBL),其充当分隔源极和漏极的绝缘层。同时,孔径允许栅极区域下方的垂直电流流动。,在上面重新生长非有意掺杂的 (uid)-GaN 沟道、AlGaN 异质结构和 GaN 帽或 p-GaN,从而构建垂直晶体管的存取区和横向 HEMT 的沟道区。这些器件采用 III-V 族工艺生产线制造。 可以使用与横向 GaN 技术相同的有源和无源元件。图 1b 显示了完全加工的 2 英寸 GaN-on-GaN 晶圆,未来也可以在更大直径上实现。图 2a 和 c) 显示了该技术的简化横截面和制造的 CAVET 的 TEM 横截面图像。

图 2. 采用准单片集成 HEMT 栅极驱动器级和感应 CAVET 的 CAVET 技术,a) 简化的横截面和 b) 相应的电路图。 c) a) 中以红色标记的垂直 CAVET 装置截面的 TEM 图像。图片由博多电力系统提供

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。