漏极过电压应力

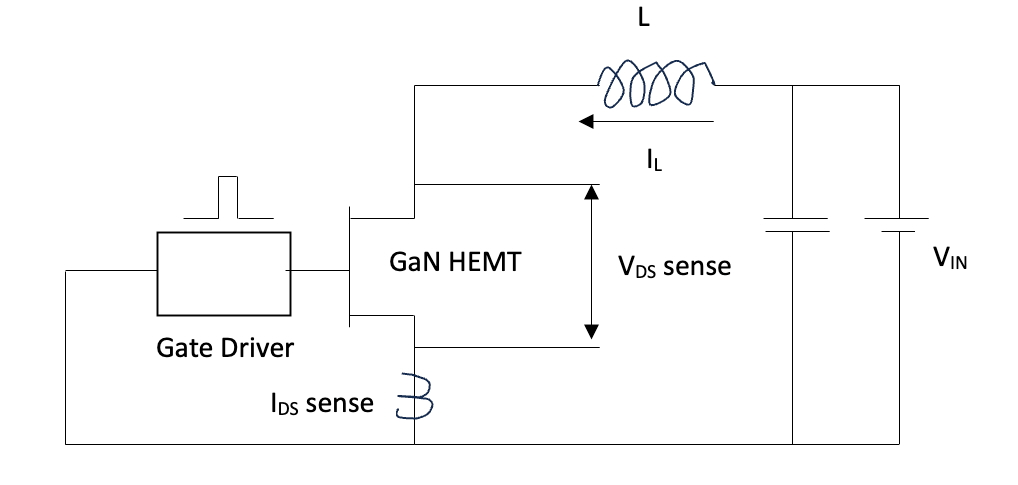

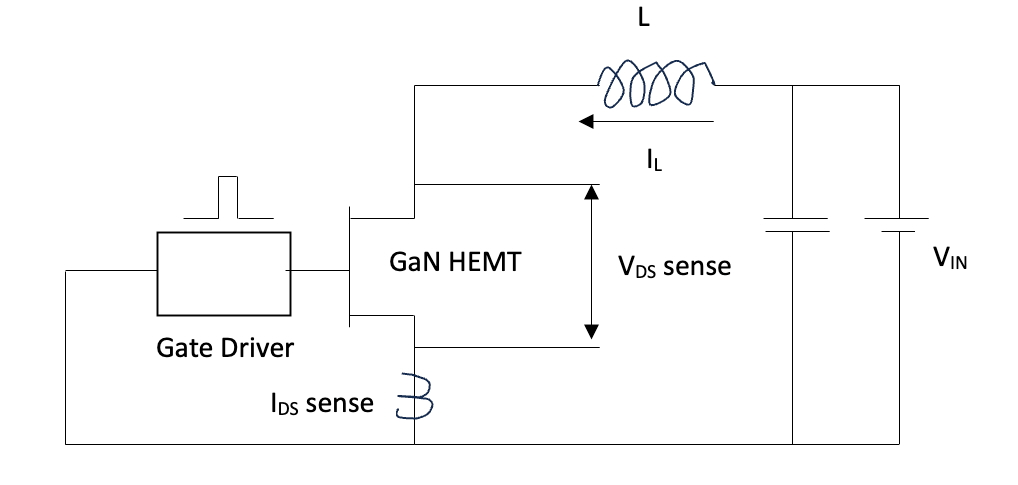

在开关转换期间,功率转换器中可能会出现漏极过电压。有多种因素会影响这些过冲的严重程度,包括正在切换的电流的转换率 (dI/dt) 以及与封装和外部连接相关的寄生电感。据报道,设备性能的下降既可以是可恢复的,可以随着时间的推移而愈合,也可以是性的。由于带负电荷的陷阱排斥沟道电子,FET 导通时的电荷俘获和关断时的去俘获会增加器件的动态导通电阻 (dRDSON)(与时间呈对数函数关系)。由于漏极结没有雪崩击穿,因此需要强调漏极过压额定值,该额定值明显超过器件的工作极限。许多制造商现在在数据表中指定了瞬态过压额定值。EPC 进行的研究在此总结,其特点是使用未钳位电感开关 (UIS) 测试装置,类似于图 1 所示的装置。

p-GaN HEMT功率器件漏栅过压失效机理分析

图 1:用于 dRDSON 表征的 UIS 测试设置示例

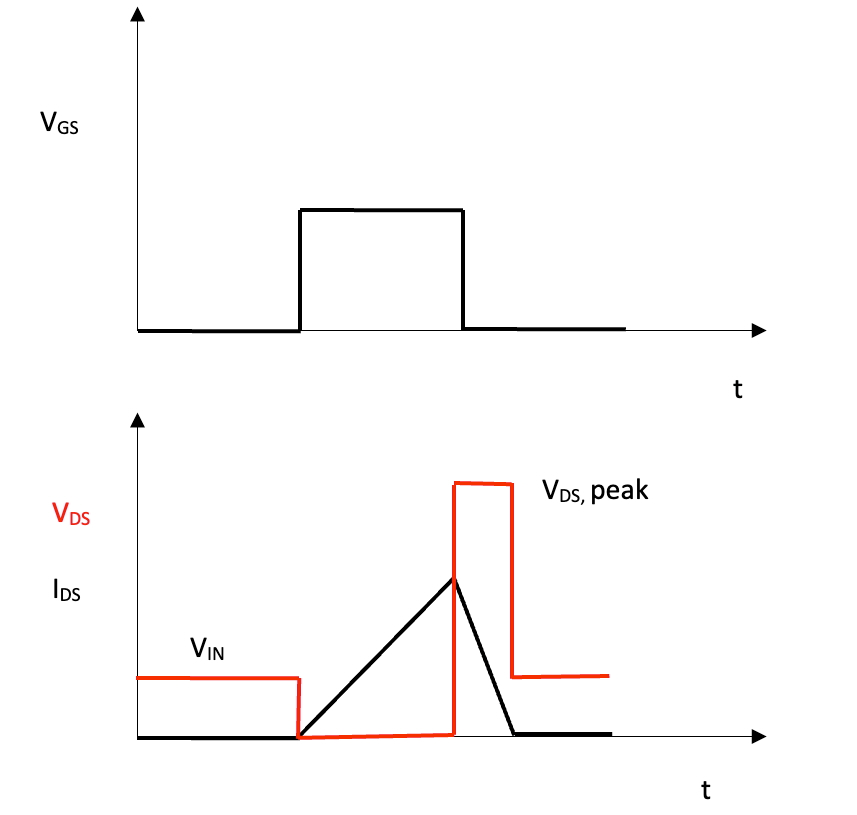

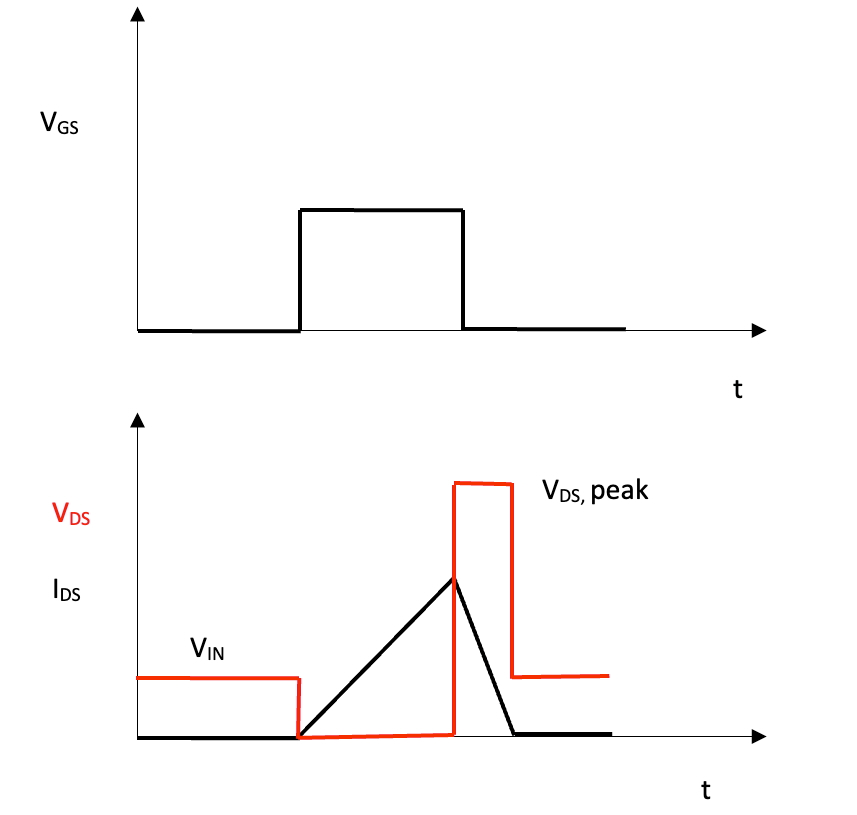

UIS 测试中常见的电压和电流波形如图 2 所示。当被测设备 (DUT) 关闭时。漏极电压尖峰上升至电压 V DS,peak直至电流放电。在 p 栅极 GaN HEMT 中,UIS 放电是通过电感器和器件输出电容之间实现的谐振实现的,从而产生第三象限传导。

p-GaN HEMT功率器件漏栅过压失效机理分析

图 2:UIS 测试波形示例

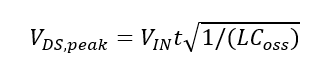

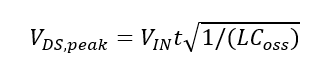

V DS,peak的大小可以表示为

p-GaN HEMT功率器件漏栅过压失效机理分析

其中 V IN是静态 V DS电压,t 是电感充电时间,L 是电感值,C oss是 GaN DUT 输出电容。对于固定的 t,V DS,peak可以通过 V IN的值进行调整。

本研究中使用的 DUT 是 EPC2218,它是一款额定电压为 100 V、 3.2 mΩ、25 °CR DSON GaN HEMT。 DUT 漏极电压 V DS通过同轴电缆测量,漏极电流 I DS通过分流器测量。使用 771 nH 的小型空芯电感器可实现 100 kHz 的重复 UIS 测试频率。 6% 的占空比用于限制 DUT 自热。使用比例积分微分 (PID) 功率电阻系统将 DUT 温度控制在 75 °C。据估计,热阻对 DUT 结温的影响。测试设置使用 LabVIEW 以 2 分钟的间隔记录所有波形。使用 MATLAB 处理电压和电流的增量提取(ΔV DS、ΔI DS )。然后从 500 个相邻样本中创建平均 R DSON提取。该方法消除了测量中的背景噪声。

来自 3 个不同批次的总共 9 个器件在 V DS、峰值电压 120 V 和 150 V 下进行了测试。120 V 测试持续了超过 4 小时,大约进行了 15 亿次循环。

UIS 测试结果和模型预测

在 120 V 应力条件下,部件的 R DSON从 75 °C 时的初始值 3.2 mΩ 逐渐增加到整个测试周期后的约 4 mΩ。这低于 75 °C 时数据表的限制 4.3 mΩ。在 150 V 应力条件下, R DSON增加要大得多,部件很快就会漂移超过数据表限制,并在测试期间结束于略高于 5 mΩ。两种情况下 R DSON的变化都是可恢复的,表明电荷去捕获。

基于 AlGaN/钝化界面处的自限制电子捕获创建了一个模型。 120 V 和 150 V 情况下的不同行为建模如下:

在 120 V 时,捕获的电荷 Q s远低于二维电子气 (2-DEG) 沟道电荷 Q p。动态 R DSON增加是由漏极接触附近的存取区域中的电子俘获引起的,其电阻与净电荷 (Q p -Q s )成反比。使用此方法,可以使用 log-t 预测 R DSON的线性相关性,这与收集的数据相匹配。该模型预测,在 100 kHz、额定电压的 120% 条件下连续过压开关 25 年期间, R DSON增加不到 10% 。

在 150 V 时,Q s接近 Q p,线性模型不再成立。基于漏极接触处的峰值电场和捕获电荷引起的势垒高度变化,开发了更复杂的模型。对测量数据进行数值拟合,可以与实际看到的 R DSON增加的进展进行良好匹配。

栅极过压应力

与 Si MOSFET 器件不同,p 栅极 GaN HEMT 器件中的栅极故障不能通过经典的瞬态电介质击穿 (TDDB) 故障机制很好地建模。高质量氮化硅 (Si 3 N 4 ) 钝化通常用在肖特基栅极金属上方,HEMT 中的击穿场远低于该薄膜的平面击穿强度。为了更仔细地检查故障机制,EPC 进行的研究使用了“智能”高温栅极偏置 (HTGB) 测试系统,对 32 个 EPC2252 DUT 进行了原位栅极泄漏 (I GSS ) 监测。在此自动化测试设置中,LabVIEW 用于控制栅极偏置 V GS并监控 I GSS 。使用正栅极应力和负栅极应力。使用的正偏压为 7-10 V,远高于额定 V GS 6 V。负栅极偏压应力也达到 -12 V,远超过 -4 V 额定值。还定期进行离线测试,以表征完整数据表参数,包括阈值电压 (V TH ) 和 R DSON。通过扫描电子显微镜(SEM)、透射电子显微镜(TEM)、光束诱导电阻变化(OBIRCH)和发射显微镜(EMMI)进行失效分析。

测试结果和故障模型

仅在 V GS为正值时才会出现故障。这也直接与纯 TDDB 机制相矛盾,因为如果是这种情况,则相反,穿过电介质的相同电场强度会导致类似的故障率。累积故障率与时间的威布尔图显示,在 8 V 和 9 V 的较低偏压下有 2 个独特的斜率,而在 10 V 偏压下只有一个斜率。有关结果的更多详细信息总结如下:

在较低的 8、9 VV GS偏置下,在较长时间间隔的威布尔图中可以看到 k = 0.5 的较浅斜率。在较短的时间间隔内,观察到更陡的斜率 k = 1.3。在 10 V 偏压下,故障分布中仅可见 k = 1.3 斜率。

k = 1.3 故障对应于硬击穿 (HBD),即电阻性栅源短路。 k = 0.5 仍然对应于 HBD 故障,但它作为中间步骤从软击穿 (SFBD) 转变,表现为正向 I GSS 增加。

这些故障中的大多数仍然具有正常的 V TH,显示出随应力的轻微正向变化,而 R DSON基本上没有变化。这表明 2-DEG 通道似乎基本上不受应力影响。

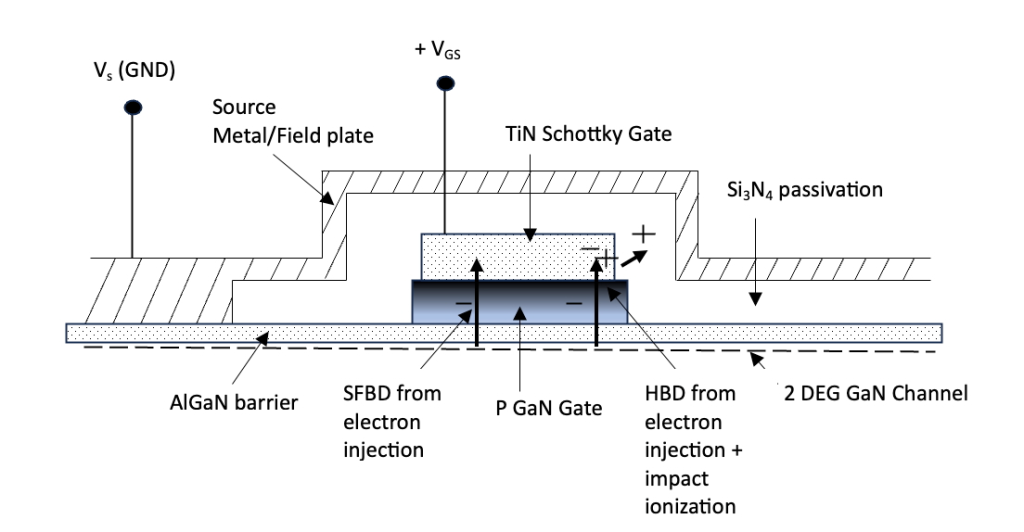

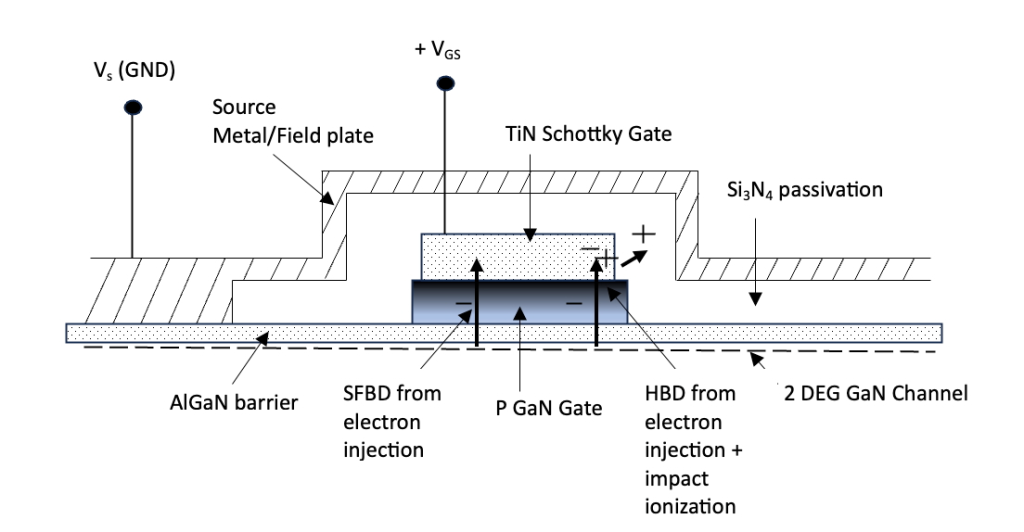

EMMI 分析显示了整个芯片中从栅极线发出的热点,而 SFBD 的 SEM 分析显示了 p-GaN/TiN 界面处的损坏。 HBD 故障的 TEM 图像显示栅极边缘处的电介质故障。

符合故障分析的结果以及收集的电气数据的解释可以通过图 3 进行解释。

p-GaN HEMT功率器件漏栅过压失效机理分析

图 3:描述栅极过压故障机制的 p-GaN HEMT 横截面

SFBD 故障可归因于从 2-DEG 通道到栅极的电子轰击,损坏了肖特基 TiN/p-GaN 接触。触点本质上变得更具欧姆性,从而导致更大的 I GSS。 HBD 故障是注入电子进入栅极区域时碰撞电离的结果。由此产生的电子-空穴对导致空穴在栅极金属/p-GaN 界面处积累。由于正电场,它们的一部分向场板移动并被捕获在介电层中。这种不断增长的正电荷会产生高局部场,终导致栅极角附近发生灾难性的介电击穿。这两种机制相互作用,使得 SFBD 为注入电子创建了一条阻力较小的路径,从而导致可用于碰撞电离的数量减少。 SFBD 增加的电流还会增加 pin 异质结(p-GaN/AlGaN 势垒/2DEG 通道)两端的压降,从而导致 TiN/p-GaN 肖特基结两端的电压更小。这些效应有效地保护电介质免受 HBD 的影响。因此,在 8 V 较低 V GS偏压下表现出 SFBD (k = 0.5)的器件的平均故障时间 (MTTF) 比 k = 1.3 器件长 3 倍以上。在较高偏压下,碰撞电离占主导地位,在 10 V 电压下,故障均归因于 HBD 电介质击穿。

为基于 k = 1.3 斜率预测 MTTF 而创建的模型显示出与实验数据的良好拟合,该模型预测当 V GS为 5 V(推荐的工作偏置条件)时,故障率为 100 ppm,使用寿命为 25 年。

结论