这个表达式有N项,就称之为N阶FFE,代表当前bit的电平,受到自身及前(N-1) bits的影响。在高速串行中应用广泛的“预加重/去加重“(Pre/De-emphasis)技术,就是一个二阶的FFE,它会根据当前bit和前1 bit的逻辑状态,来调整当前bit的电平。

发送端均衡

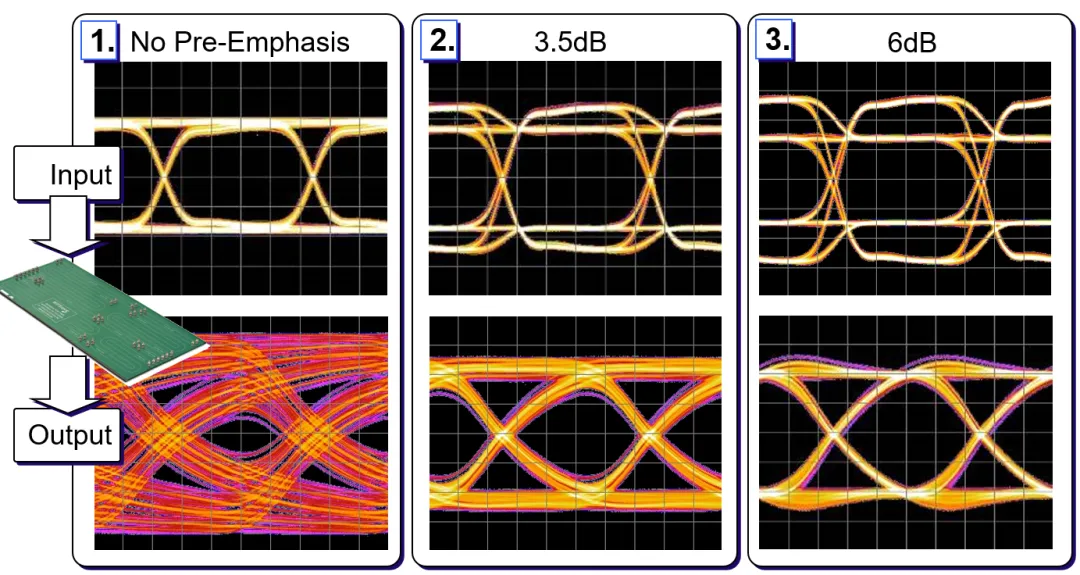

我们来看一个Pre-emphasis的真实。当发送端的信号不做任何处理时,发送端眼图是很完美的;一旦信号经过长背板传输之后,严重的ISI抖动会导致眼图几乎闭合(例1)。当发送端增加3.5dB预加重时,会将频率较高的跳变沿信号(Transition Bits,指的是与前一bit逻辑状态不同的bit,如01码型中的1,或110码型中的0等)的幅度增强3.5dB。这些预先的增强会部分抵消长背板的损耗,从而不同码型的电平在到达接收端时基本相等,ISI抖动就大幅降低了。接收端的眼图无论是眼高眼宽,还是抖动,都有非常明显的改善(例2)。

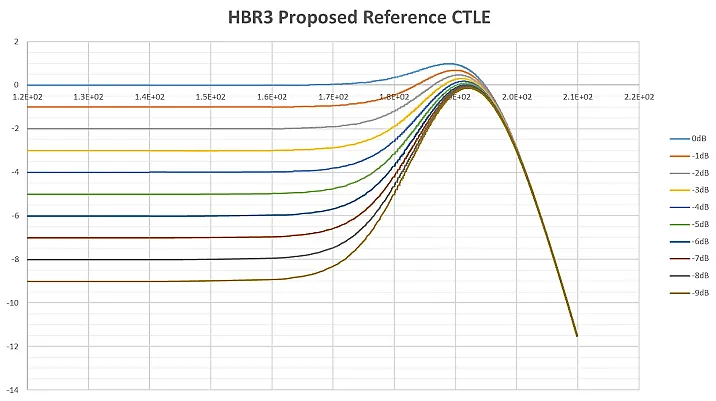

CTLE的实现方法和FIR滤波器有点像,实现的是一个近似带通滤波器的效果。下图是一组典型的CTLE滤波器,低频衰减大,而高频衰减小。这个滤波曲线,和传输链路的损耗正好形成互补(传输链路插入损耗是低频衰减小,而高频衰减大)。在接收端,实现了不同频率间均匀的总体损耗,从而降低了ISI抖动。CTLE和DFE/FFE不同,它不依赖参考时钟,在连续时间域上对信号进行均衡;而DFE/FFE是数字域上的均衡,必须要先有参考时钟,来区分不同的bit,才能进行均衡。接收端常常使用CTLE和DFE的组合,先用CTLE打开近乎闭合的眼图,恢复出时钟,再用DFE进一步均衡补偿。

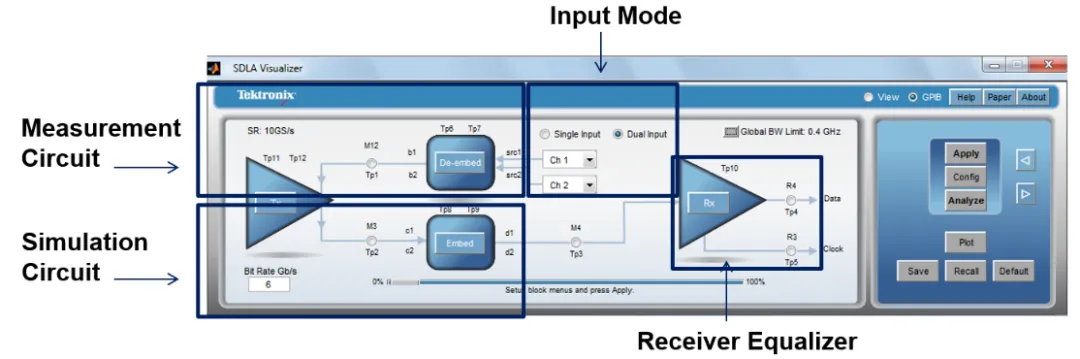

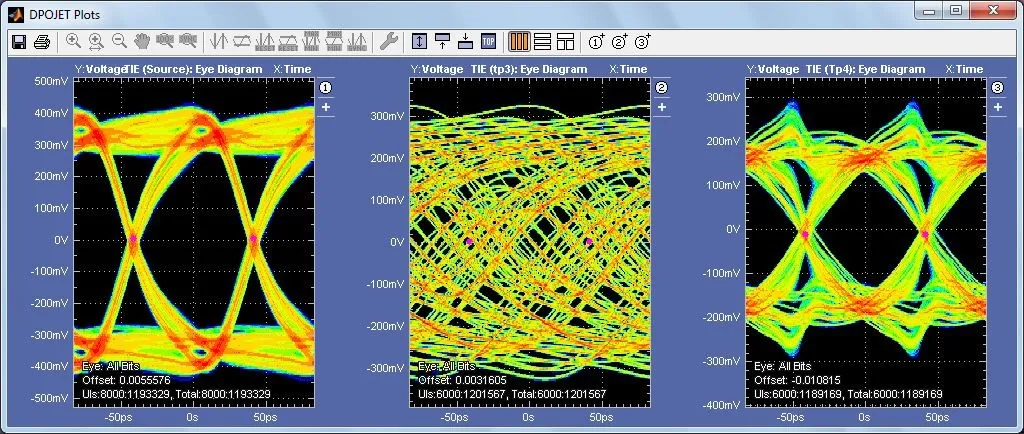

设计工程师为了解决ISI问题,常常需要在链路损耗和均衡技术之间做出综合考虑。泰克的SDLA软件可以模拟发送端的Tx EQ和接收端的Rx EQ,还能模拟传输链路的不同损耗。

让你在产品设计的初期,就能预估链路的ISI抖动,探索和尝试的均衡组合以降低ISI抖动,大幅减少产品研发的时间。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。