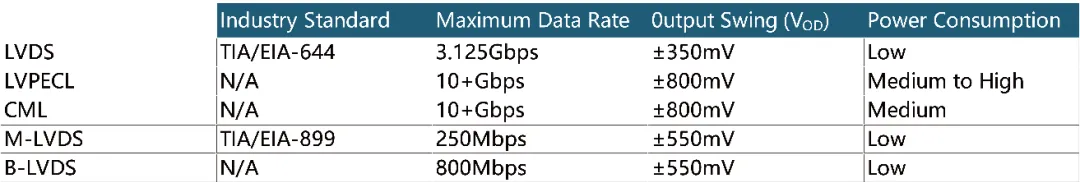

LVDS(Low-Voltage Differential Signaling ,低电压差分信号)是美国国家半导体(National Semiconductor, NS,现TI)于1994年提出的一种信号传输模式的电平标准,它采用极低的电压摆幅传输高速差分数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰等优点,已经被广泛应用于串行高速数据通讯的各个场合,比较广为人知的有笔记本电脑的液晶显示,数据转换器(ADC/DAC)的高速数字信号传输,汽车电子的视频码流传输等。

LVDS(Low-Voltage Differential Signaling ,低电压差分信号)是美国国家半导体(National Semiconductor, NS,现TI)于1994年提出的一种信号传输模式的电平标准,它采用极低的电压摆幅传输高速差分数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰等优点,已经被广泛应用于串行高速数据通讯的各个场合,比较广为人知的有笔记本电脑的液晶显示,数据转换器(ADC/DAC)的高速数字信号传输,汽车电子的视频码流传输等。

高速信号传输的实际应用

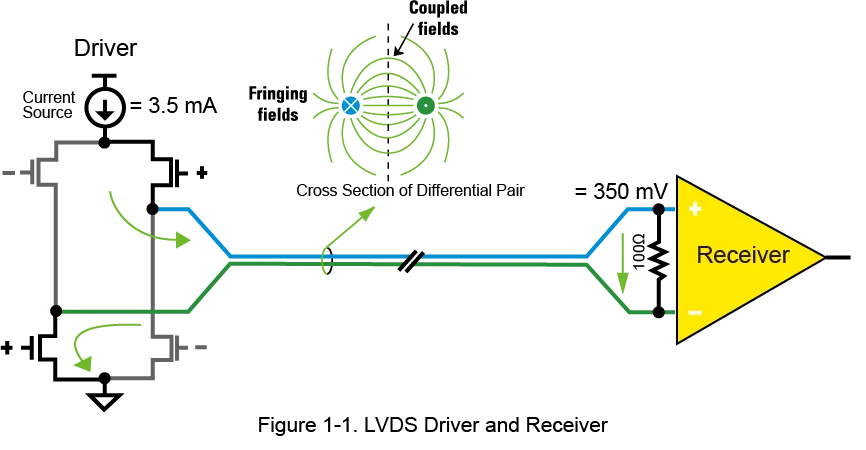

LVDS是一种电流驱动的高速信号,在发送端施加一个3.5mA的恒定电流源。控制开关管的通断,就可以使得发送端流向接收端的电流,在正向和反向之间不断变化,从而在接收端的100欧姆差分负载上实现+/-350mV的差分电压变化,可实现3.125Gbps的高速数据传输。LVDS采用差分线的传输方式,会带来几个显著的优势:● c. 极低的电压摆幅,功耗极低

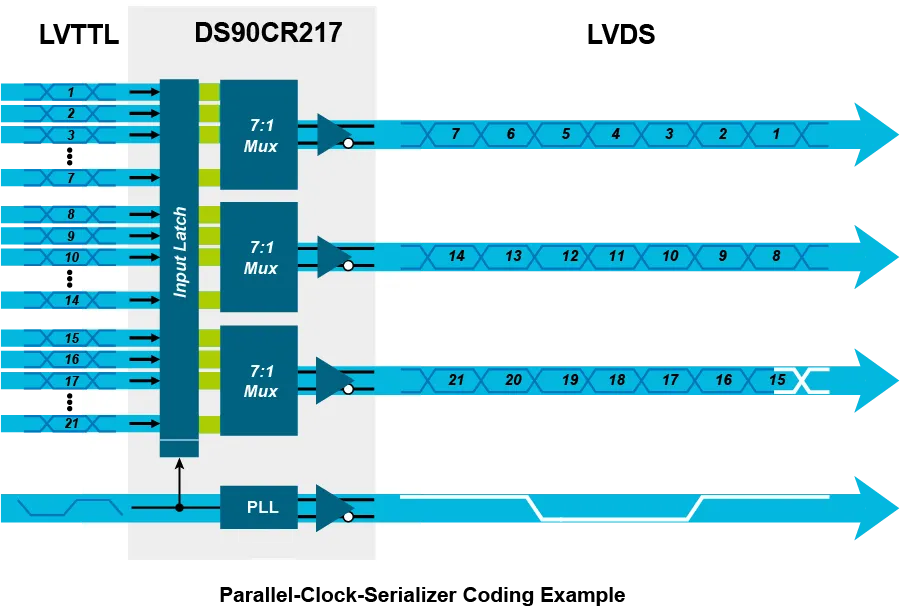

传统的LVDS采用同步时钟的方式,使用一对差分时钟,为多三对数据信号提供时钟参考。每个时钟周期内,每对数据传输7 bits信息。需要用到SerDes芯片,在发送时,将并行信号通过并/串转换,变成高速串行信号;在接收到高速串行信号时,使用串/并转换,还原并行信号。

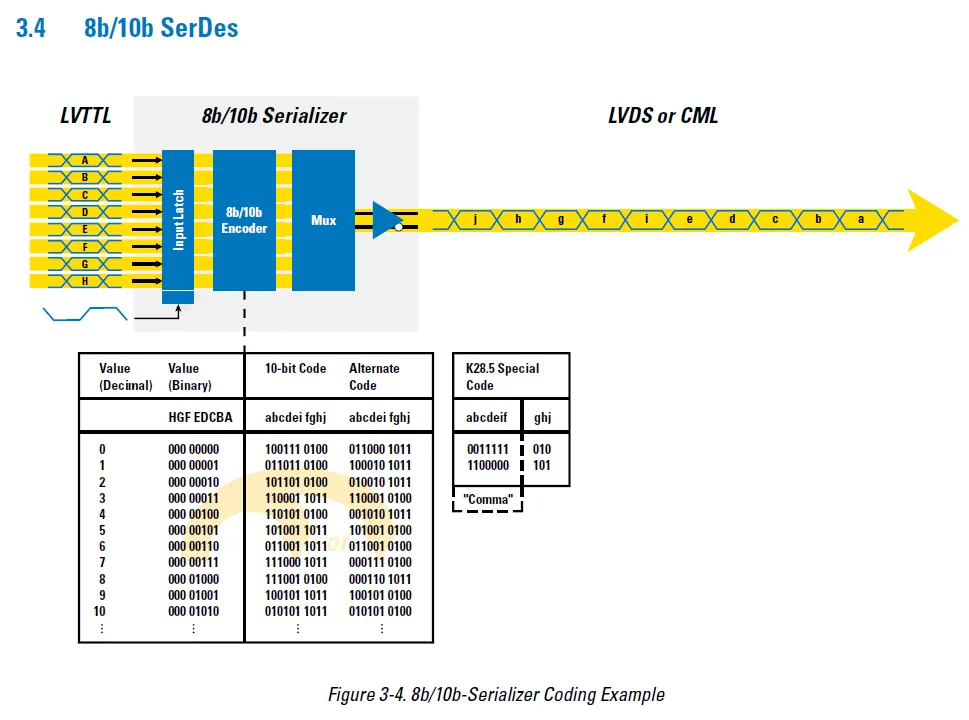

在收到信号后,通过锁相环(PLL)从数据里恢复出时钟。这种传输架构称之为嵌入式时钟(Embeded Clock)。8b/10b编码还可以让传输信号实现直流平衡(DC Balance),即1的个数和0的个数基本维持相等。直流平衡的传输链路可以串联隔直电容,提升链路的噪声和抖动性能。嵌入式时钟和8b/10b被广泛用于工业高速传输标准,比如PCIe,SATA, USB3等,也包括JESD204 (CML)。

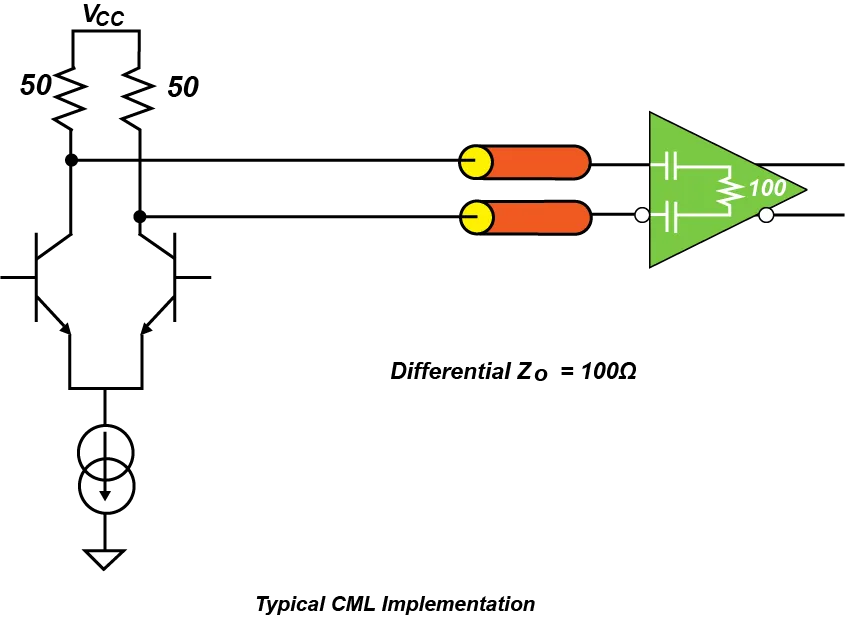

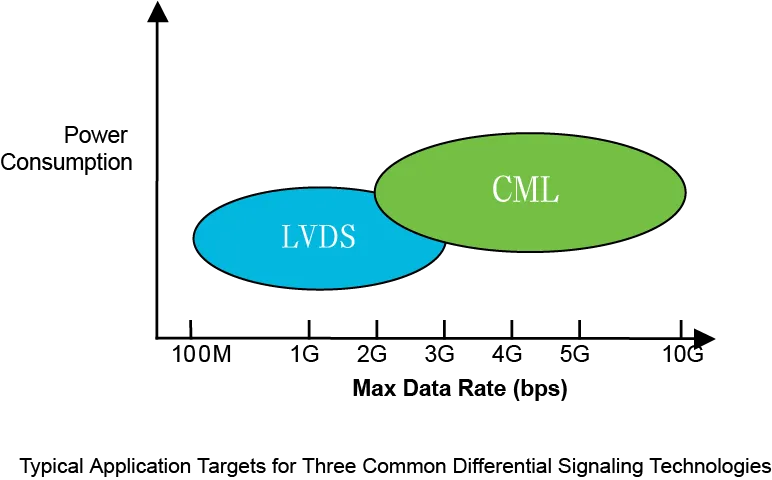

不同于LVDS的是, CML(Current-Mode Logic)采用电压驱动的方式,在源端施加一个恒定的电压Vcc。通过控制开关管的通断,接收端就可以得到变化的差分电压。CML使用嵌入式时钟和8b/10b编码,工作电压比LVDS更高,同时在发送和接收芯片里使用均衡技术,以确保高速、长距离传输时仍具有很的误码率。使用CML技术的JESD204B可支持高达12.5Gbps的data rate,其的C版本甚至可以支持高达32Gbps data rate。

那么我们在设计高速接口芯片时,到底应该使用LVDS还是CML(JESD204)呢?简单的原则是,CML速率更高,而LVDS则功耗更低。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。