锁相环(Phase-Locked Loop,PLL)是一种电子电路,用于在输入信号和参考信号之间建立特定相位关系的控制系统。它通常由相位比较器、环路滤波器、振荡器和分频器等组成。以下是锁相环的基本概念:

负反馈环路:整个锁相环构成了一个负反馈环路,通过不断地调节振荡器的频率,使得输入信号和参考信号之间的相位差化,从而实现锁相环的目标。

2 锁相环的基本单元电路

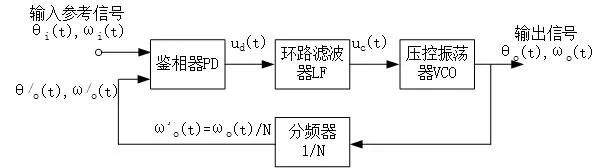

加入分频器的锁相环由鉴相器(Phase Detector,PD)、环路低通滤波器(Loop Filter,LF)、压控振荡器(Voltage Controlled Oscillator,VCO)和分频器(Frequency Divider)组成。输入信号的相位和频率分别为θi(t)和ωi(t),单位分别为rad和rad/s;输出信号的相位和频率分别为θo(t)和ωo(t),单位分别为rad和rad/s。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。