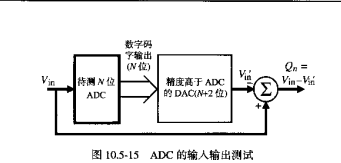

如果 ADC 是理想的,(Q,的值将限制在±0.5LSB之间。输入输出测试可以用来测量失调误差、增益误差、INL和DNL。

图10.5-16给出了一个4位 ADC可能的曲线。图上标出了INL 和DNL误差。以模拟轴为参考的非线性误差用单位斜线的高度来表示。增益误差将表现为随着V的增加,锯齿曲线的增加或减少为一常量。失调误差是从OLSB线向上或向下的固定的平移量。

理想情况下, 图10.5-16应该等于 ADC的量化噪声。当位数增加时,图10.5-16 所示的个别细节是不可能看到的, 除非将水平坐标放得很大。一般人们会在±0.5LSB 处画出水平线以观察这些线以外的趋势。必须通过比较正峰值和负峰值来确定 DNL。注意,在模拟输入为21/32时,ADC非单调。随着位数的增大,观察INL、失调和增益误差将变得更容易。

如果使用一个纯正弦波发生器,输入输出测试的重建输出信号V可以通过失真分析仪或频谱分析仪来确定ADC的动态范围。

为了不产生任何非线性失真,动态范围至少为6NdB,这里N是ADC的位数。这个测量使用了的设置,只是码型发生器被无谐波正弦波发生器驱动的ADC所取代、如果输入的正弦波不纯,那么它的谐波可能掩盖 ADC的非线性。同样,这个测量中使用的 DAC 必须比 ADC 更。

另一种进行上述测试的方法是将被测ADC的数字输出编码存储在一个 RAM缓冲器中。在测量后,缓冲器的内容用快速傅里叶变换(FFT)进行后处理来分析量化噪声和失真分量。

给出了这种被称为FFT测试的建立方法。这种测试强调了转换器的非线性,根据时钟频率的不同它可以是静态的或动态的。由ADC的非线性引起的输人信号的谐波分量将在ADC的基带频谱上引起混叠。应该保证正弦输入信号与这些谐波不一致。

当使用FFT测试时一定要当心。当诸如量化噪声等小信号出现在与信号不同的频率上时,它们的频谱被主信号的泄漏所掩盖,因而不可能地得到SNR。因此,一个从有间采样获得的FFT并不能很好地估计原始信号的功率谱,这个问题可以通过一个窗口来解决[11]。“升余弦窗”

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。