另一种方法是可以适当地划分每个子 DAC 的基准电压,再将所有的单个模拟输出相加,第二种方法综合了各种按比例缩放的方法,从而可得到每种缩放方法的性能。相同缩放类型DAC的组合

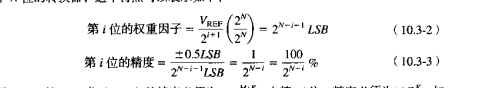

图10.3-1给出了用M位子DAC和K位子DAC实现M+K位DAC的方法。这里,我们认为两个子 DAC使用了同样的按比例缩放方法。一个子DAC转换M个MSB位,另一个DAC转换K个LSB位. LSB之 DAC 的模拟输出除以?2?以进行适当的缩放。合并后的子 DAC 的模拟输出可以表示为:

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。