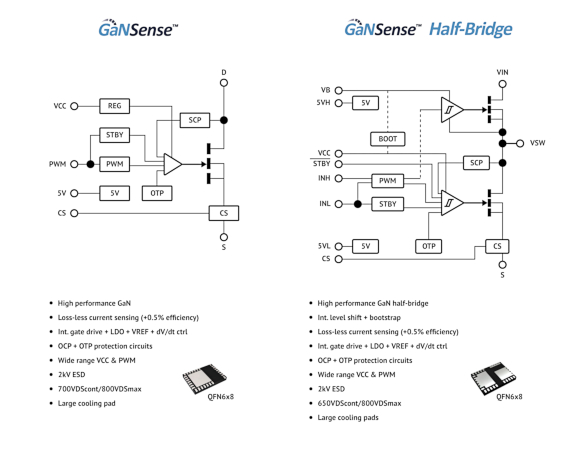

对减小电源尺寸的需求不断增长,不断挑战该行业生产越来越高的效率和功率密度。由于硅器件达到其频率限制(<100 kHz),提高硅基电源性能的能力已经放缓,这阻碍了电路拓扑和磁性设计的进一步优化。新兴GaN 宽带隙器件由于 QG 栅极电荷降低 15 倍、Qoss 输出电荷降低 16 倍以及开关速度提高,效率和尺寸显着提高。GaNSense 电源 IC 集成了可靠、稳健设计所需的所有缺失要素,使这些设备终走出实验室,进入现实世界的快速充电器和适配器。其中包括 GaNSense 功率 IC 和 GaNSense 半桥 IC 中的集成栅极驱动、稳压栅极电压、无损电流感应和保护功能(图 1)。这些产品支持新的电路拓扑,业界正在利用它们来推进更小、更高效的设计。

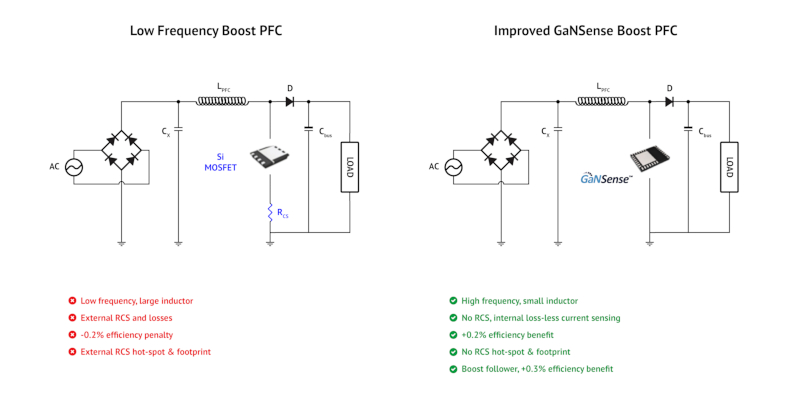

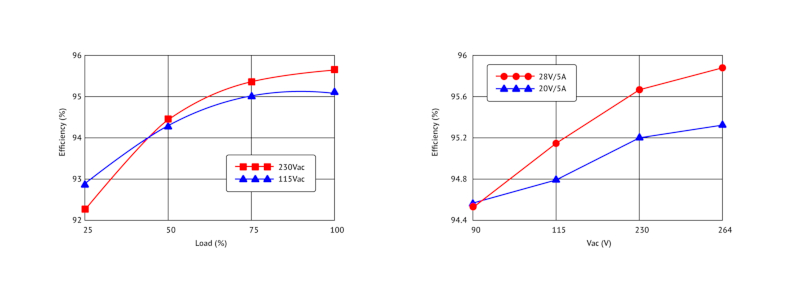

可以添加升压跟随器功能以进一步提高效率,以便直流母线在低压线路交流输入期间以较低的电压运行。这样可以降低峰值电流水平、降低负电流和循环能量以及降低磁芯损耗(图 3)。所有这些改进相结合可额外带来 +0.3% 的效率优势。

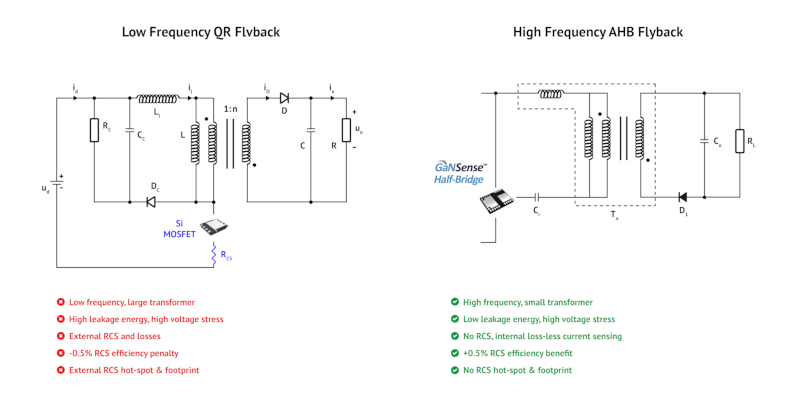

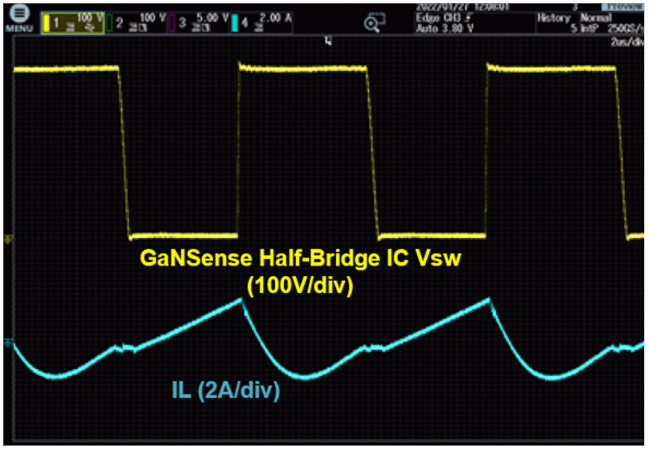

准谐振反激式由于其宽电压增益能力而成为下游转换器的流行拓扑。然而,当功率水平增加到 100 W 以上时,变压器泄漏能量显着增加。随着泄漏能量的增加,初级开关和次级 SR 开关上的电压应力也会增加,包括更高的电压尖峰和EMI 噪声。此外,USB供电规范修订版3.1支持更高的输出电压水平,例如28V至48V,这使得反激变压器匝数比的设计更加困难。初级和次级上的电压应力远高于传统的 20 V 输出条件。非对称半桥反激式转换器采用初级侧开关的零电压开关 (ZVS) 和次级侧整流器的零电流开关 (ZCS) 运行。此外,初级开关被钳位在PFC处输出电压通常约为 400 V,因此应力和电压振铃问题得到显着缓解。出于这些原因,AHB 拓扑是 PD 3.1 应用的,而 GaNSense 半桥 IC 可以实现小变压器尺寸的高频操作和无损电流感应,从而实现更高的效率(图 4)。

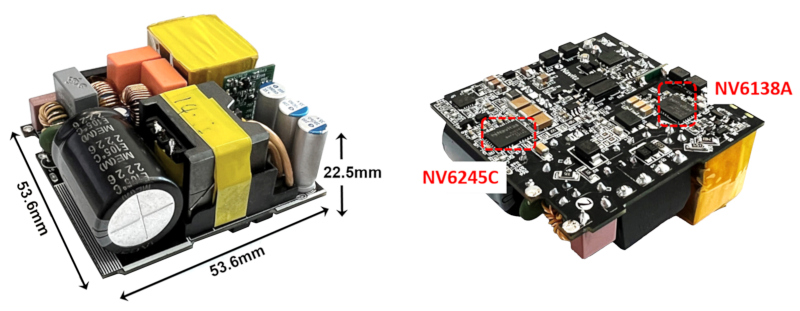

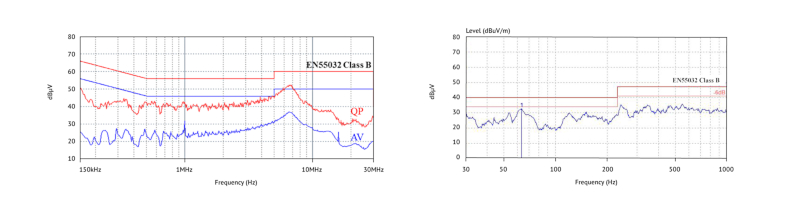

完整的 PFC+AHB 140 W、PD 3.1 评估板 (EVB)(图 5)已经构建并测试了功能和性能。该设计实现了令人印象深刻的 100 cc 估计外壳尺寸,功率密度为 1.4 W/cc。EVB 包括优化的 PFC、AHB 和 SR 功率级和磁性器件,并使用现成的控制器。PFC 和 AHB 电源系围绕 NV6138A GaNSense 电源 IC 和 NV6245C GaNSense 半桥 IC 设计。EVB 还包括EMI 滤波并通过传导和辐射发射。

满载升压PFC波形如图 6 所示。在 115 VAC 线路输入期间,升压电路在零电压开关 (ZVS) 条件下工作,其中升压开关节点电压 (VSW) 在 GaN 功率 FET 导通之前降至零。每个开关周期。在 230 VAC 线路输入期间,升压电路在部分 ZVS 条件下运行,其中 VSW 下降至约 100 V,然后从该处硬切换至零。控制器在关断期间自动检测 VSW 节点的谷值,以便在每个开关周期再次开启,以尽可能优化电压水平的开启点,从而限度地减少硬开关损耗。由于 GaN 功率 IC 具有非常低的输出电容,因此漏极电压将在每个周期快速降至谷值。控制器必须具有快速谷值检测功能,以确保在 VSW 电压恢复之前在点开启。升压跟随器功能还可以在低线电压条件下直流母线电压降低至 300 VDC 以及高线电压条件下升高至 400 VDC 时发挥作用。

图 6. 满负载条件下的升压 PFC 开关波形,115 VAC 输入(左)、230 VAC 输入(右),IL=蓝色(1 A/格),VDS=黄色(100 V/格)。图片由博多电力系统提供

效率曲线(图 8)显示 4 点效率和负载效率。该设计在 90 VAC 输入条件下实现了惊人的 94.5% 满载效率,比的产品至少高出 1%,节能高达 20%。90 VAC 和满负载时的效率决定了终适配器产品的外壳尺寸和外壳接触温度。

,传导和辐射 EMI始终是电源设计的一个主要问题。由于更快的开关速度和频率,采用 GaN 的新设计不断受到 EMI 挑战的质疑。设计人员通常在设计接近完成阶段时才解决其设计的 EMI 部分,结果却惊讶地发现排放远远超出了允许的限制。该设计的 EMI 扫描(图 9)显示,传导 EMI 和辐射 EMI 均远低于限制,并且具有足够的制造公差余量。这些结果可以通过在设计阶段尽早实施适当的 EMI 指南来实现,其中包括 PCB 接地层、电感器屏蔽、正确设计的 EMI 滤波器组件、正确的 PCB 平面规划以及组件位置和邻近度等良好实践。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。