两种损失

原则上,功率半导体有两种损耗:通态损耗和开关损耗。后者包括开通和关断损耗。通态损耗由电流、通态电压(对于 MOSFET,由其 R DSon)和占空比决定。在描述功率半导体的几个参数中,所谓的特征开关频率暗示了有用的开关频率。为了估计效率和设计冷却,总损耗是决定性的。因此,开关损耗在不同方面都很重要。先前在同一设置中进行的测试表明,栅极

电阻器对开关损耗的影响有限,并且导通损耗超过了关断损耗。这里,反向恢复电荷Q rr的影响分析了开通损耗W on 。

MOSFET 导通时

二极管关断

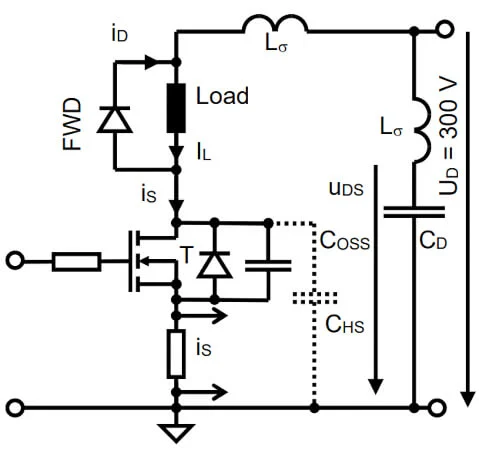

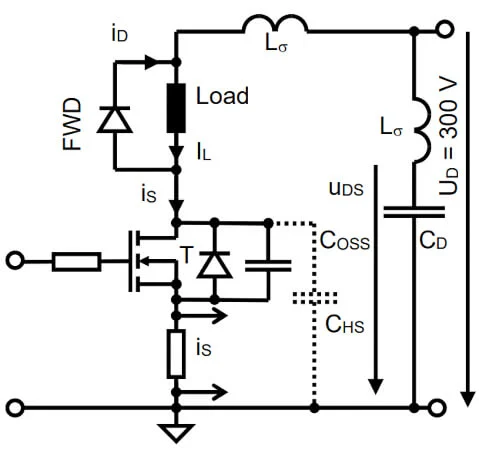

MOSFET 的一种典型应用是用作低侧单开关和电感负载(见图 1)。导通时,负载电流 I L流过负载,关断时,MOSFET 负载电流换向至续流二极管 (FWD)。该电流在 MOSFET 下次导通时返回至 MOSFET。MOSFET 的关断就是 FWD 的导通,反之亦然。因此,二极管的关断影响MOSFET的导通。

图 1 显示了杂散电感 L σ, 它对于 MOSFET 关断时的电压过冲非常重要。

图1 试验台示意图。图片由博多电力系统提供

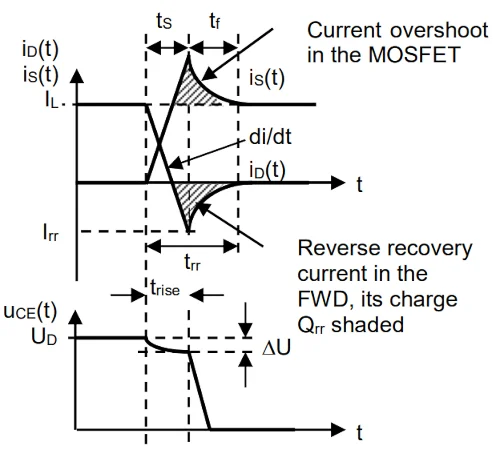

双极二极管的关断行为

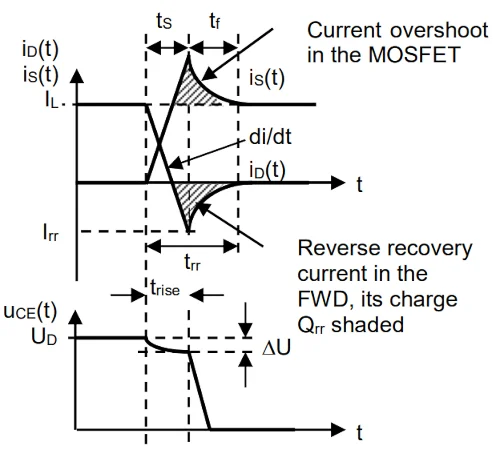

在二极管关断时,电流以确定的斜率 di/dt 减小。在双极二极管中,电流变为零后,它进一步减小到负值,直到二极管中的移动载流子重新组合,从而产生负电流 I rr以及反向恢复电荷 Q rr。当二极管电流向其峰值反向值I rr减小时 ,存储时间t S过去。移动载流子重新组合后,二极管获得阻断电压的能力 [1] [2]。因此,MOSFET 必须在 t S内承受(接近)直流电压 U D(参见图 2)。

这会导致 MOSFET 导通损耗较高。在反向恢复峰值之后,反向恢复电流下降时间tf开始。两个时间加起来就是反向恢复时间t rr。

trr=tS+tf(1)

由于负载电流 I L在这些短开关转换期间几乎保持恒定,因此二极管的反向恢复电流会导致 MOSFET 中出现电流过冲(见图 2)。该额外电流还会导致 MOSFET 产生额外损耗。

二极管的关断行为取决于多个参数,例如关断时的 di/dt、负载电流、温度以及二极管类型 [2]。实际上,峰值反向电流 I rr可能高于负载电流 I L (见图 4)。

图 2. MOSFET 关断和导通时二极管行为的原理一致性。图片由博多电力系统提供

二极管电流关断时的高 di/dt 会在杂散电感 L σ中感应出电压,从而导致 EMC 问题。因此,对于双极二极管,人们尝试通过降低 tf 期间的 di/dt(从而增加 t f )来赋予它们“更软”的关断行为。关断行为可以通过 t f和 t S的比率(给出因子 S,称为“快速因子”[3])区分为“软”和“快速”。软因素[4][2]:

S=tftS=trr?tStS=trrtS?1

S+1=trrtStStrr=1S+1(2)

由于二极管关断行为对于开关(MOSFET 或其他技术)至关重要,因此进行了多次尝试来改进它 [5]。不幸的是,Q rr的减小会增大导通电压[2]。

肖特基二极管的关断行为

具有近乎理想开关波形的二极管是肖特基二极管(见图 5)。这是一种没有 PN 结但具有构建耗尽区的金属-半导体接触的单极二极管。对于硅,阈值电压低于双极二极管,约为 300 – 400 mV。非常小的恢复电荷是电容性的,是由反向电压导致的耗尽区的增长引起的。遗憾的是,由硅制成的肖特基二极管的阻断电压仅限于 200 V 左右 [2] [3]。

理论损耗计算

计算在电压 U D下开关电流 I L的 MOSFET 的开关损耗能量 W on和 W off的理论方法是其中 W OSS是存储在输出电容 C OSS中的能量。该杂散电容在 MOSFET 关断时充电至 U D 。导通时,MOSFET 会缩短该容量。因此,C OSS的放电电流无法通过图 1 中所示的

分流器来测量。对于所使用的 MOSFET,C OSS被指定为 48 pF,从而在 300 V 时产生 2.2 ?J。通常,与 W 相比,该能量较小在 (表格1)。然而,应该检查是否有更高的电压,因为它取决于 U D 的平方,并且从漏极到地的容量可以通过散热器的容量 C HS来增加(图 1)。C HS的放电在电流 i S中可见 (图 1)。

Won=t上升?UD?IL2

Woff=tfall?UD?IL2

WCOSS=COSS?U2D2(3)

应该记住,在 W on和 W off 的公式中,因子 1/2 是因为计算了三角形的面积,而对于 W COSS,该因子是由于

电容器公式的积分而产生的。

开关损耗功率 P VS是能量 W on和 W off与开关频率的乘积。

从图2给出的曲线可以看出,在导通时,电压略微降低了D U , D U 是杂散电感L σ和电流斜率di/dt 的乘积。实际上,这些杂散电感必须保持较小,以提供安全关断和低电压过冲。

从图2中可以看出,当MOSFET承受全电压U D时,有一部分反向恢复电荷Q rr流过MOSFET 。这持续 t S。因此,理论上,导通时的额外损耗部分是 导致二极管关断损耗的 Q rr的另一部分。然而,在实践中,这很难处理,特别是因为(2)中给出的定义有缺陷[2]。

WQrr\近似tStrr?Qrr?UD=Qrr?UDS+1(4)

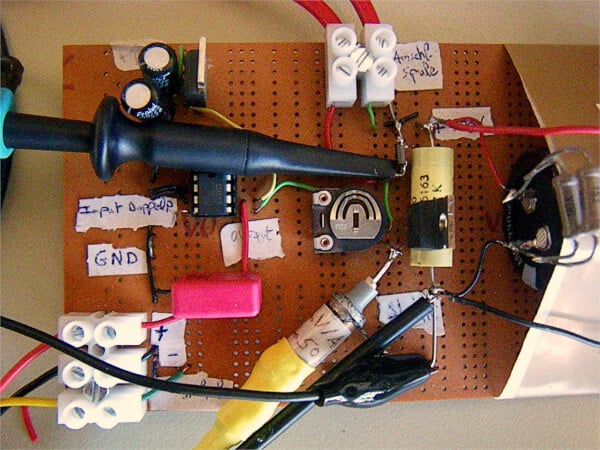

双脉冲试验台

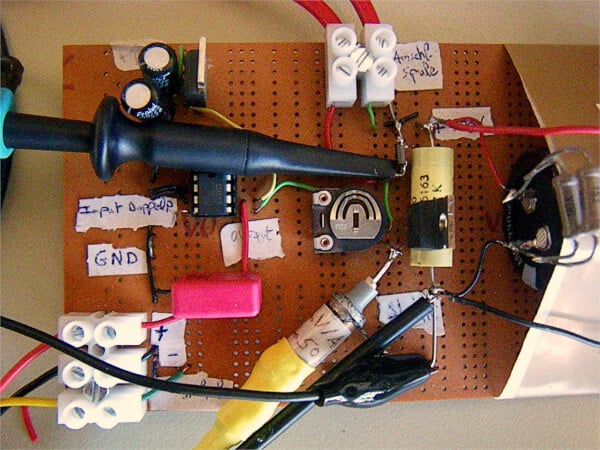

该测试台是在PCB上实现的。直流电源和双脉冲发生器位于外部,因此图 3 中未显示。为了估计杂散电感,使用标准 600 V 1 A 二极管测量了导通瞬态。如图 4 所示,源电流在 100 ns 内从 0 A 增加到 13 A,同时 MOSFET 两端的电压下降约 15 V,对应的杂散电感约为:Lδ\约15V?100ns13A=115nH(5)

图 3. 用于测量的测试台。图片由博多电力系统提供

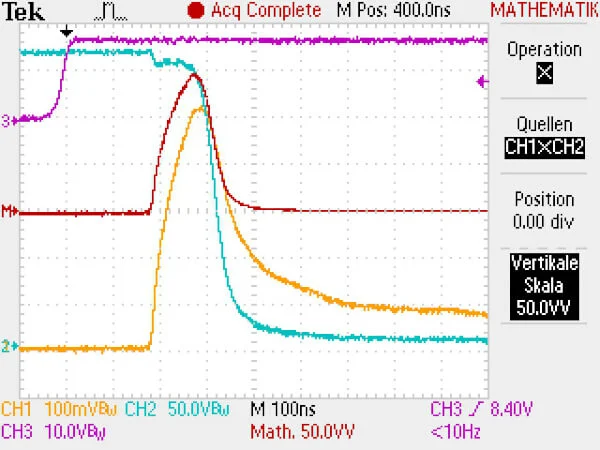

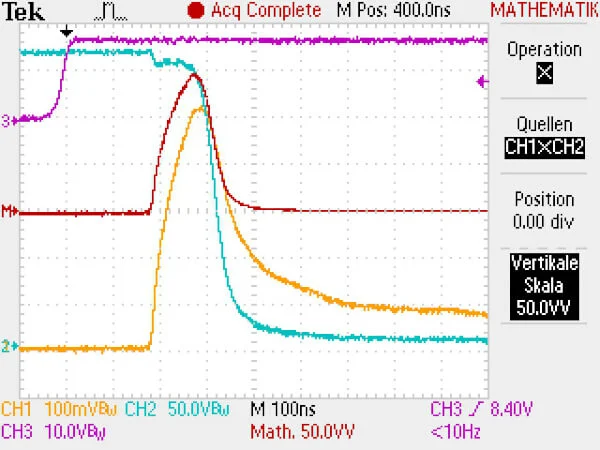

通过该杂散电感,导通时的电流增加被限制为 U D /L σ = 2.6 kA/μs。然而,这超出了 MOSFET 的能力。从图 4 中可以看出,通过高反向电流 i rr和长 t rr,所使用的 600 V 1 A 双极标准二极管并不是该应用的选择。该测量中的带宽限制仅用于说明,W on、W off和 Q rr的所有测量都是在 100 MHz 的全带宽下进行的。

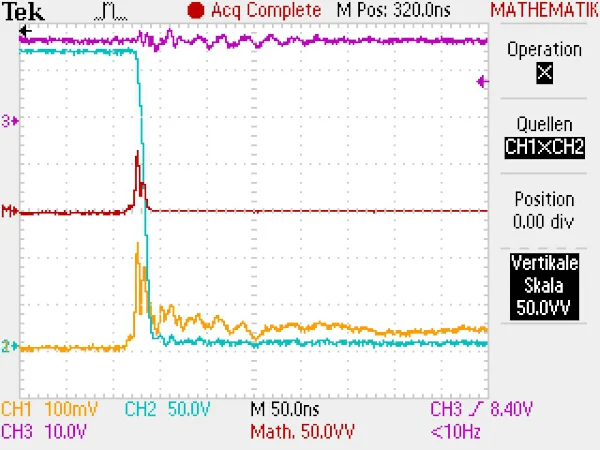

图 4. 使用 600V 1A 双极标准二极管作为 FWD 的 MOSFET 的导通行为,带宽限制仅用于更好的测量,时间 100ns/Div CH1:i S 2.5 A/Div,CH2:u DS 50 V/ Div,CH3:第二个脉冲的触发信号 MATH = CH1 X CH2:p V (t) 1250 W / Div。图片由博多电力系统提供 [PDF]

损耗能量和 Q rr的测量

如图 1 所示,在 MOSFET 的源极连接中放置了一个为 50 Ω 提供 40 mV/A 电流的分流器。使用 10:1 探头测量漏源电压,并将两者乘以示波器 MATH 功能。与图 3 相比,使用了示波器的完整 100 MHz 带宽。这些数据以“逗号分隔值”(“CSV”)形式导出,并在 PC 上使用图表计算程序进行进一步分析。每个测量点的瞬时功率 pV(t) 乘以时间间隔 Dt,并在开关转换期间求和,分别得到 W on。W关闭。

为了测量 Q rr ,从 t rr期间测得的源电流 i S 中减去I L = 1 A的负载电流。所有高于负载电流的源电流均由 Q rr驱动 (图 2)。

这部分电流乘以时间间隔Δt即可得到电荷,并从 i S > 1 A 到 i S = 1 A求和。 这样就计算出了Q rr 。

测试台中使用的二极管

对于用作 FWD 的不同类型的二极管,在 300 V、1 A 和室温下测量了二极管反向恢复电荷 Q rr以及 MOSFET 导通损耗能量 W on 。所有续流二极管的 MOSFET 均保持不变。结果按照反向恢复电荷Q rr增加的顺序在表1中给出。

对于所使用的 MOSFET,数据表中给出了 23 ns 的上升时间,根据等式 (3),在 300 V、1 A 电流下,W 导通电流为 3.5 J 。下面显示的 W on测量值更高(对于双极二极管,更高)并且很大程度上取决于FWD 的Q rr 。

个尝试是 600 V 1 A 双极标准二极管,因为它的额定值符合要求。不幸的是,它提供了非常大的 I rr和 Q rr(图 4),导致 MOSFET 的导通损耗很高。1000 V 1 A 双极标准二极管也会出现同样的情况。

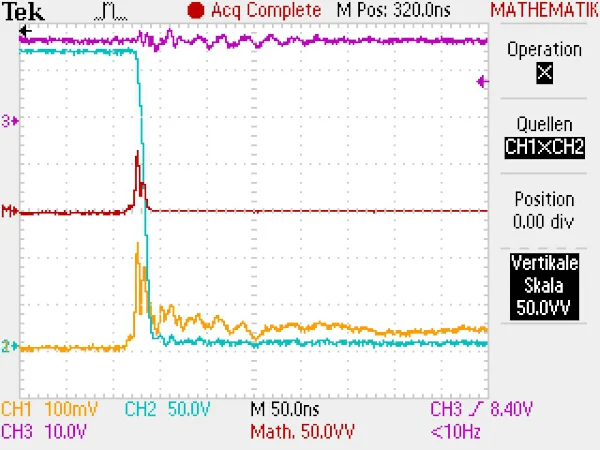

图 5. 具有用作 FWD 的 600 V 2 A SiC-肖特基二极管的 MOSFET 的导通行为,全带宽,时间 50ns/Div CH1:i S 2.5 A/Div,CH2:u DS 50 V/Div ,数学 = CH1 X CH2:pV(t) 1250 W/Div。图片由博多电力系统提供 [PDF]

更好的选择是快速双极二极管。所测试的 600 V 1 A 型仍在生产,而 1500 V 1 A 型属于过时型(但性能仍然良好)。

由于 MOSFET 经常用于桥式拓扑,因此测试了第二个相同类型 MOSFET 中的体二极管。它具有较低的 I rr和 Q rr,导致比标准双极二极管更低的 W on,但性能不如两个快速双极二极管。

测试了两种类型的肖特基二极管。首先,串联三个 150 V 1 A Si-肖特基二极管。使用这种串联连接是因为没有可用的 600 V Si-肖特基二极管。3 * 150 V = 450 V 的阻断能力足以满足实验目的。与生产中的快速双极二极管相比, Q rr增加了大约 6% ,但 W on减少了 17%。本次测试中使用的二极管是 600 V 2 A SiC-肖特基二极管。它给出了迄今为止测试的二极管中 Q rr和 W on的值。

表 1. 测量的 Q rr、测量的 W on以及通过方程 (6) 得出的 W on近似值

测试了 600 V 1 A 标准二极管的并联连接和三个 150 V 1 A Si-肖特基二极管的串联连接。这个想法是至少部分电流流过肖特基二极管,因此关断行为将介于标准二极管和肖特基二极管之间。 然而,与单独的标准二极管相比,这仅使 Q rr减少约 3% ,但 W on增加约 5% 。这将在测量的公差范围内。与单独的 600 V 1 A 标准二极管相比,这种微小的差异并不奇怪,因为在三个肖特基二极管的串联中,它们的阈值电压也被增加,因此只有很少的电流流过它们。

将相同的 600 V 1 A 双极标准二极管与仍在生产的快速双极二极管类型并联,效果更好。这里,阈值电压相似,因此一定量的电流应该流过快速二极管。与慢速标准二极管相比, Q rr减少约 11% ,但 W on只减少约 5% 。

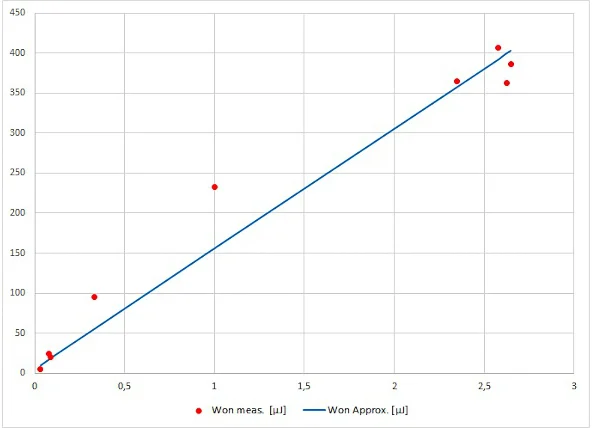

通过 Q rr和 U D近似 W on

MOSFET 导通损耗能量 W Qrr的计算公式为:(4)计算困难。因此,根据公式trise、 I L、 U D、 C OSS和 Q rr来近似估计完整的开通损耗。(6) 制成。

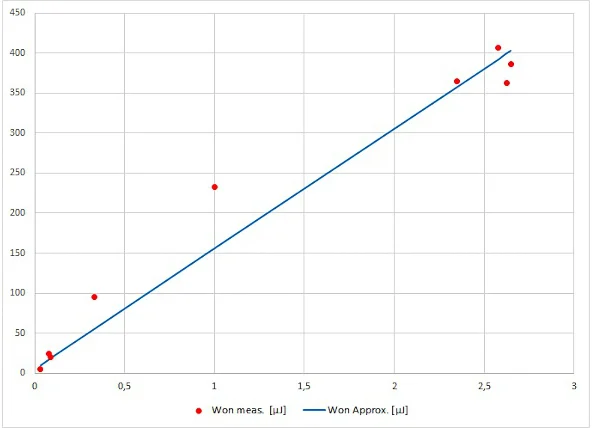

图 6. 测得的 W on(红点)及其根据方程 (6)(蓝线)的近似值,作为测得的 Qrr 的函数。图片由博多电力系统提供 .

Won≈t上升?UD?IL2+COSS?U2D2+Qrr?UD2(6)

假设 Q rr的一半在全电压下流过 MOSFET,从而在其中产生能量损失。对于线性斜率,这对应于因子 S = 1,请参见公式 (2) 和图 2。因此,公式 (6) 一项中的因子 ? 表示 t S /t rr,并且应与以下注释进行比较公式 (3) 给出的因子。对于 t上升,使用数据表中的值 (145 ns)。如果存在容量 C HS(见图 1),则应将其添加到等式(6)中的 C OSS 中。

表 1(右列)中还给出了方程 (6) 的结果值。有时,各个测量值与根据等式(6)计算的值不同。然而,如果测量值和计算值显示在同一图表中,则可以看出方程(6)至少给出了有用的近似值。必须记住,(6) 中使用的 Q rr是测量值,而不是数据表值。

近似方程 (6) 给出了 W对Q rr的线性依赖性,但图 6 中测量值的插值将具有弯曲的曲率。一种可能的解释是,通过缩短载流子寿命来降低 Q rr的制造措施使二极管具有更快速的反向恢复行为,因此改变了 t S /t rr的比率。

肖特基二极管总结 特别是与双极续流二极管一起使用时,MOSFET 的导通能量高于理论计算值。续流二极管存储的电荷对 MOSFET 的开通损耗有很大影响。这很重要,特别是在高开关频率的应用中。因此,使用快速双极或肖特基二极管可以降低MOSFET的总损耗。

标准双极与快速双极二极管的分立并联仅具有很小的优势,而双极标准二极管与三个 Si-肖特基二极管串联的分立并联给出了稍小的 Qrr,但也稍微增加了W。

与肖特基二极管一起,杂散电容 C OSS造成的损耗可能相当大,特别是如果散热器有额外的电容 C HS的话。