所有

存储器类型都可以分为易失性或非易失性。当设备断电时,易失性存储器会丢失其内容,而非易失性存储器即使在断电时也能保留存储的信息。

随机存取存储器 (RAM) 系列包括两种重要类型,即静态 RAM 和动态 RAM,它们都是易失性的。嵌入式系统中广泛使用的两个非易失性存储器示例是 EEPROM 和闪存。

尽管 EEPROM 和闪存具有非易失性的优点,但与 RAM 芯片相比,它们的写入周期明显更长。例如,典型 EEPROM 的写入周期在 1-10 ms 范围内,而典型 SRAM 的访问时间约为 70 ns(根据Cypress Semiconductor 的说法,快速 SRAM 提供的访问时间在 10 ns 范围内) 。

写入周期比读取周期长得多,使得 EEPROM 和闪存适合存储器读取操作次数远多于所需写入操作次数的应用。

另一方面,销售点 (POS) 终端、网络处理引擎和服务器等应用需要具有快速读写周期的非易失性存储器。在这些情况下,我们可以使用传统的 SRAM 存储器以及备用

电池和一些控制电路来创建快速非易失性存储器。

这些非易失性存储器通常称为电池供电的 SRAM。

电池供电的 SRAM

电池支持的 SRAM (BBSRAM) 采用电池作为替代

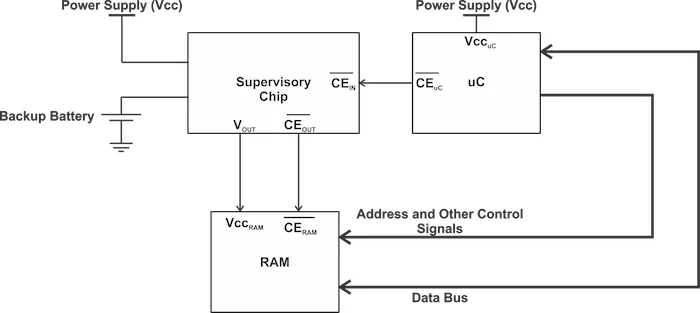

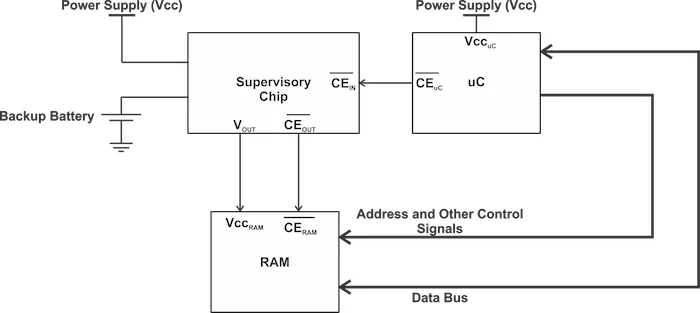

电源,以在电源故障期间保留内存内容。基本思想如图 1 所示。

BBSRAM 在断电时保留设备的内存。

图 1. BBSRAM 在发生电源故障时保留设备的内存。

主电源 (V cc ) 和电池应用于监控 V cc是否超出容差条件的监控芯片。在正常工作模式期间,V cc出现在监控芯片的输出端(V out),为SRAM 供电。然而,如果发生电源故障,则使用电池为 SRAM 供电。

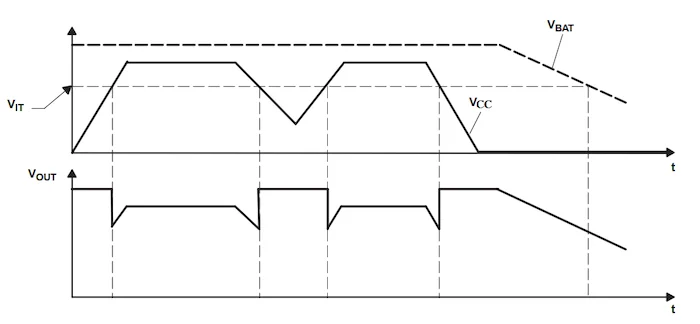

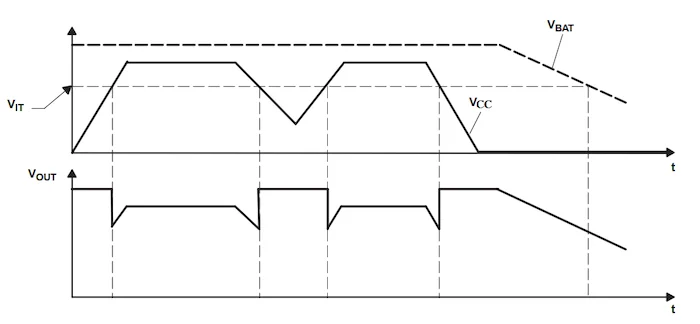

以下时序图说明了TPS3617的操作,TPS3617 是一款 5V 电源监控芯片。

TPS3617 的时序图

图 2. TPS3617 的时序图。图片由德州仪器 (TI)提供

当 V cc降至工厂调整阈值(TPS3617 为 4.55 V)以下时,输出 V out从 V cc切换到 V BAT。

BBSRAM 的数据保留

数据保留是非易失性设备可以保留其内容的长时间。对于 BBSRAM,数据保留主要取决于电池寿命。为了限度地延长电池寿命,我们需要在电池工作模式下消耗尽可能少的电流。

如图1所示,我们可以使用监控芯片来控制SRAM的芯片使能输入$$\frac{}{CE_{RAM}}$$,并在需要时将其置于待机模式。请注意,SRAM 只需消耗很小的漏电流(小于约 10 μA)即可在待机模式下保留数据。

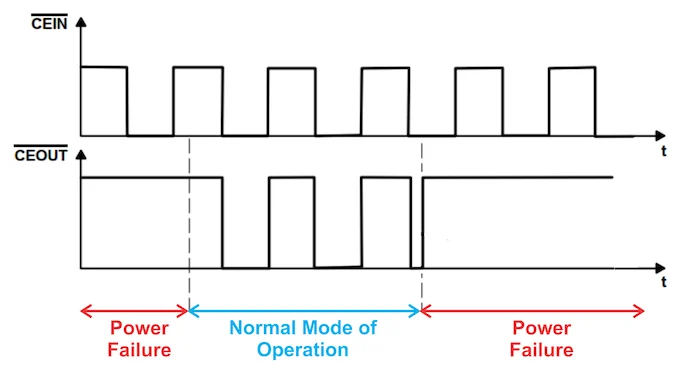

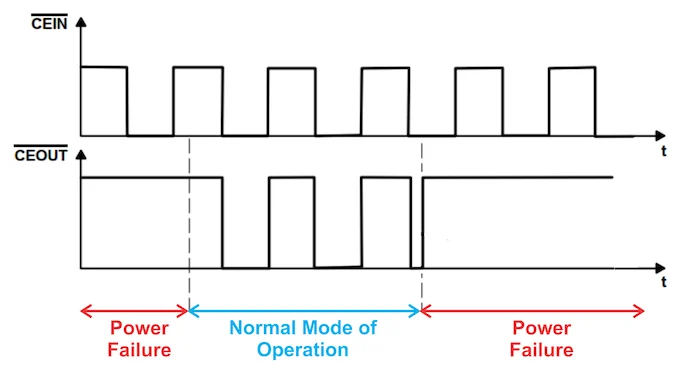

在正常操作模式期间,监控芯片将由微控制器控制的 $$\frac{}{CE_{IN}}$$ 的所有转换传递给 $$\frac{}{CE_{OUT}}$ $。因此,通常情况下,监控芯片是透明的,MCU 可以启用/禁用 SRAM。然而,在电源故障期间,监控芯片将 $$\frac{}{CE_{RAM}}$$ 设置为逻辑高电平,以使 SRAM 进入待机模式。

图 3 对此进行了说明。

如果发生电源故障,当监控芯片将 CE_RAM 设置为逻辑高电平时,SRAM 将进入待机模式。

图 3.如果发生电源故障,当监控芯片将 $$\frac{}{CE_{RAM}}$$ 设置为逻辑高电平时,SRAM 将进入待机模式。图片(已修改)由德州仪器 (TI)提供

将 SRAM 置于待机模式可限度地降低电池模式下的功耗。这样,典型的BBSRAM可以具有大约10年的数据保留。

值得一提的是,电池寿命可能会受到内存待机电流消耗以外的其他机制的影响,即通过卷边密封造成的电池电解液损失。电解质的损失速度在高温下加速。

例如,在 85°C 时,即使完全不连接负载,电池也会在大约两年内完全耗尽。因此,我们需要考虑电池容量、内存电流要求和环境温度,以便对电池寿命进行现实的预测。

避免错误的写周期

我们上面讨论了禁用 SRAM 可以延长电池寿命,从而提高 BBSRAM 的数据保留时间。还需要将 SRAM 置于待机模式以避免错误的写入周期。

在图 1 中,您会注意到 MCU 由主电源 V CC供电。V CC超出容差条件可能会导致 MCU 输出出现不可预测的值。如果发生电源故障且 SRAM 未禁用,MCU 可能会向 SRAM 写入错误数据。因此,当检测到电源故障时,我们需要通过将SRAM置于待机模式来对SRAM进行写保护。

请注意,许多监控芯片控制其芯片使能输出 $$\frac{}{CE_{OUT}}$$ 的方式与图 3 所示的方式略有不同。

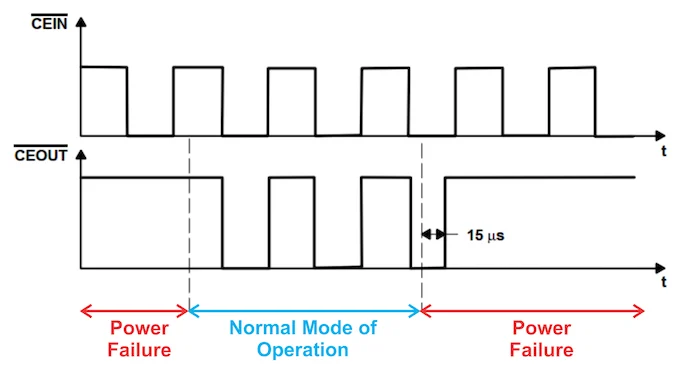

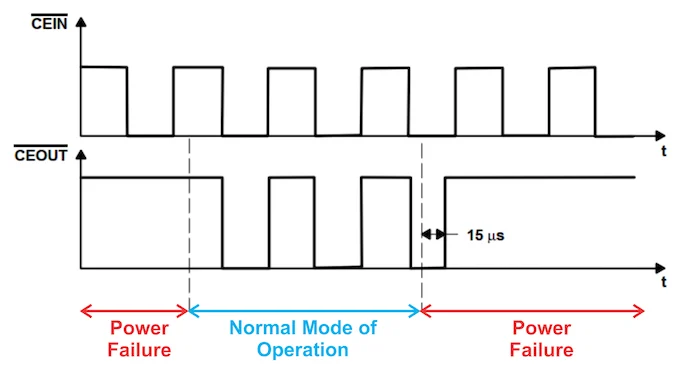

例如,图 4 显示了TPS3610如何控制 SRAM 芯片使能。

TPS3610 的芯片使能时序

图 4. TPS3610 的芯片使能时序。 图片(改编)由德州仪器 (TI)提供

可以看到,上图中的第二次断电发生在 $$\frac{}{CE_{IN}}$$ 为逻辑低电平(MCU 已启用 SRAM)时。在这种情况下,TPS3610 在延迟 15 μs 后将 SRAM 置于待机模式。实施此延迟是为了允许当前潜在的写入周期完成。

欧洲

CE

不同制造商的监控芯片通常会包含这种延迟;然而,延迟值应根据数据表进行检查,延迟值的变化范围约为 10 μs 至 15 μs。

电池供电的 SRAM 芯片

如上所述,我们可以使用监控芯片和电池来使 SRAM 表现得像非易失性 SRAM。或者,我们可以使用 BBSRAM 芯片,例如DS1225,它在单个封装中提供所有必需的元件(锂电源、控制电路和 SRAM)。

该器件监视电源是否存在任何超出容差的情况。如果发生电源故障,它会自动使用集成电池为 SRAM 供电,并将存储器置于待机模式,以防止数据损坏。该器件封装与现有 SRAM 的封装相匹配,这使得将当前存储器升级为非易失性类型变得非常容易。