焊料与烧结

基于锡 (Sn) 和铅 (Pb) 的焊料是常见的

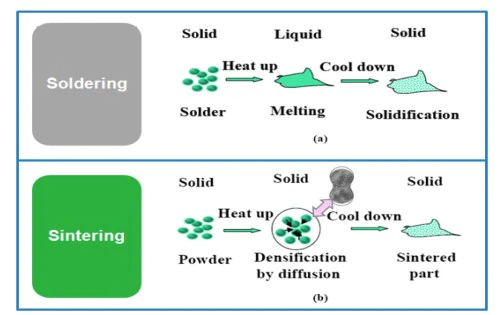

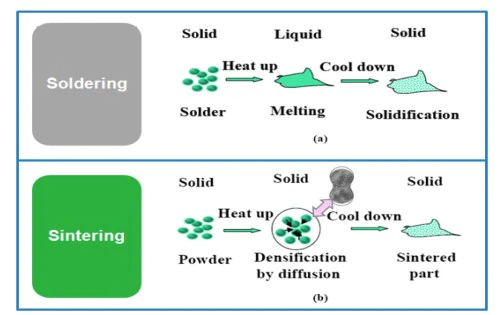

芯片粘接材料。ROHS 合规性要求用银 (Ag) 和铜 (Cu) 替代铅。焊接过程中,焊料颗粒通常在 200°C – 250°C 范围内熔化,并润湿要接触的表面。金属间相是在凝固的冷却阶段形成的。烧结是一种用低于熔点的粉末制造结构的方法。银烧结1于 1990 年首次推出,现在许多公司提供基于各种银颗粒配方的芯片粘接解决方案。烧结基于原子扩散,如图 1(a) 所示,在给定时间内结合使用热量和压力来促进向界面的扩散。与焊料不同,没有相变。

图 1(a):焊接和烧结工艺的比较(2)

如图 1(b) 所示,与普通焊料配方相比,银烧结焊膏的导电性和导热性以及高温稳定性得到了很大改善。低热膨胀系数 (CTE) 和良好的拉伸强度使其在热循环和功率循环测试中具有优势。

图 1(b):普通焊料和两种银烧结焊膏的一些材料性能比较(2)

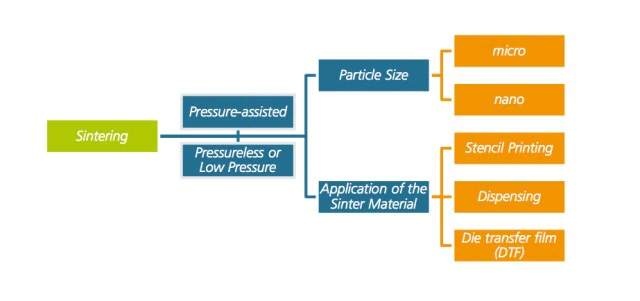

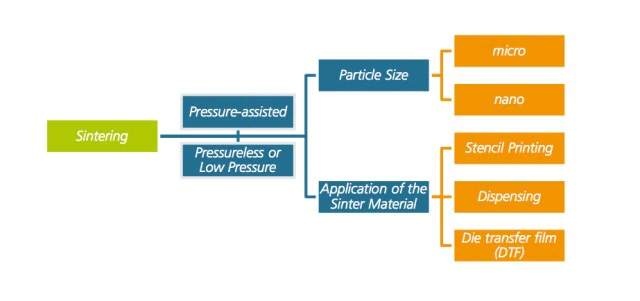

图 2 概述了烧结类型。压力辅助烧结对于 SiC

功率模块为常见。随着烧结颗粒的尺寸从微米级减小到纳米级(即< 1μm),烧结温度和时间可以降低。纳米级压力可以在 5 至 15 MPa 范围内,温度从 200°C 至 300°C,时间从 1 至 10 分钟。

2023年10月13日

图 2:烧结变化概述(C. Bayer,“电力

电子模块的未来封装技术”,Fraunhofer IISB。

图 2:烧结矿变化概述(C. Bayer,“电力电子模块的未来封装技术”, Fraunhofer IISB

烧结浆料的应用通常通过干法放置的模板印刷来完成。点胶技术相对较新,湿法放置使得该过程更容易出现错位。芯片转移薄膜 (DTF) 是芯片拾取和放置后的流程,其中首先通过初始加热和加压步骤将薄膜转移到拾取的芯片上,然后将芯片 + 烧结薄膜放置在已拾取的芯片上。施加热量和压力。

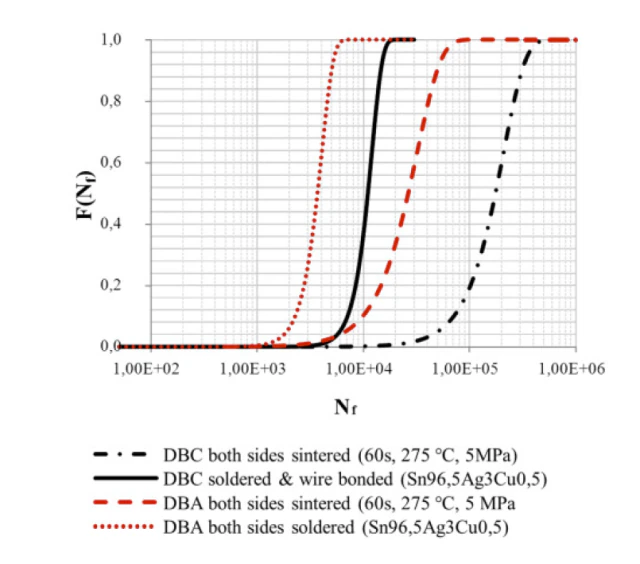

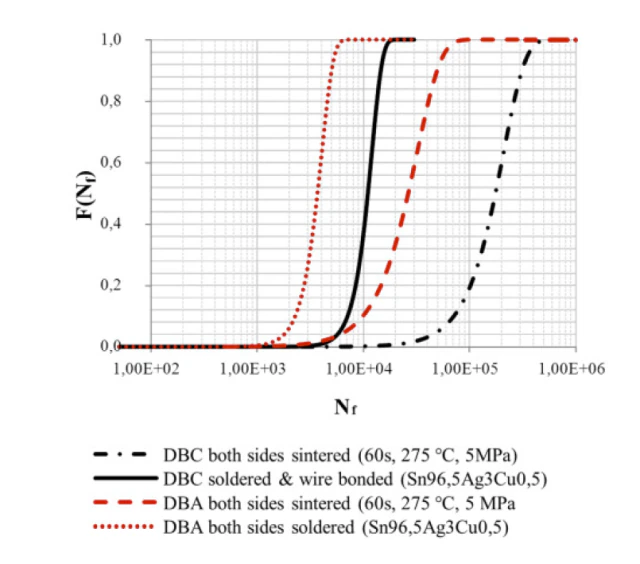

许多团队使用银烧结焊料显着改善了芯片贴装工艺的温度循环 (TCT) 和功率循环寿命。图 3 显示了这样的一个示例。在 DBC

基板上进行的主动温度循环测试中,寿命增加了 17。

图 3:主动温度循环(45°C 至 175°C)故障的威布尔分布(3)

大面积银烧结

在近举行的PCIM Europe 2023 会议上,Heraeus 产品经理 Florian Seifert 和压力烧结浆料项目负责人 Ulla Hauf 博士介绍了他们关于将银烧结浆料用于大面积烧结 (LAS) 应用的研究4。

如图 4 所示,功率模块组件中的烧结可用于:

芯片附着到基板上,例如 DCB/DBC 或活性金属钎焊 (AMB) 氮化硅。这些通常具有镍金 (Ni/Au) 表面处理。银迁移是一个问题,特别是对于高压烧结而言,需要仔细优化糊料和烧结条件以降低这种风险。

例如,在芯片顶部进行烧结可以使铜夹或金属柱取代传统的铝线接合。为了实现这一点,可以在芯片上放置金顶部金属表面处理。铜箔等后取放芯片顶部系统 (DTS)可实现重型铜线键合,与传统铝线相比,可提高热性能和可靠性能。

将基板固定到模块底板上。由于与裸芯片相比尺寸增加,这带来了新的挑战,尺寸范围可以从15×20 mm 2到>40×40 mm 2。此应用程序可归类为 LAS。

LAS 面临的一些具体挑战包括:

获得压力均匀的薄膜:更薄的烧结膜可以提高整体模块的导热率。虽然烧结在实现更薄的键合层厚度 (BLT) 方面比焊接具有特定优势,但该厚度需要随着模块尺寸的增加而增加,例如,从芯片贴装中使用的正常 <40-50 ?m 增加到 >100-50m。 150 微米。高度差会使这变得更具挑战性,因为可能需要更高的压力,从而增加芯片/

散热器机械完整性的风险。

由于基板组件内的封装材料或焊点所施加的限制,干燥过程的操作窗口可能要小得多。温度、升温速率、总时间和气氛可能都需要优化。

烧结浆料本身的化学性质可能需要进行调整,以便在上面设置的操作窗口限制下更好地工作。

成本:Ag压力辅助烧结工艺成本较高,而热界面材料(TIM)具有成本优势。烧结和 TIM 的组合有时可以在成本和性能之间提供良好的折衷。

所示的剪切强度测试结果证明了 Ag LAS 流的成功优化。与标准芯片贴装银烧结浆料相比,LAS 浆料在测试的尺寸范围内提高了 40% 以上的剪切强度。