随着硅技术的进步,ASIC 密度更高,逻辑电压随之降低。较低的电压与较高的电流要求相结合,要求

电源具有更严格的容差。从 PCB 到

芯片的电源控制是本研究的主题。使用典型旁路值的频率扫描仿真表明,分立封装

电容器并不是降低芯片电源波动的重要因素。PCB 电源上的小升压可以提供更经济的解决方案来管理器件电源。

高性能 ASIC 的封装设计包括电源层优化和封装旁路电容器的适当放置 - 在某些情况下还需要添加外部放置的分立电容器。这会产生的供电网络系统和符合规格的电压容差。本研究重点研究低

电感封装电容器在降低电源抖动方面的效果。与 I/O 电源不同,各种频率组件消耗的电流不容易确定。因此,整体电源旁路方案需要涵盖整个估计工作频率范围的容差要求。

基板有效电源电感

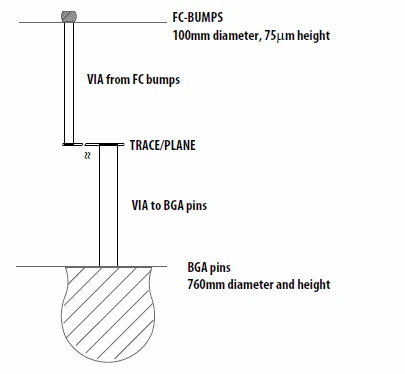

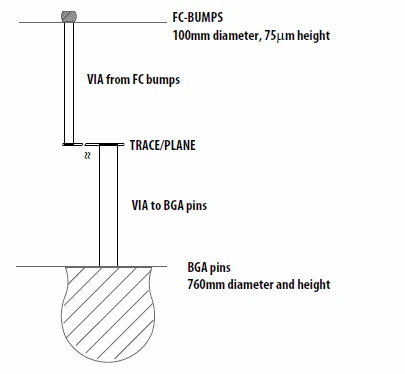

IC 封装的主要功能之一是将电源从 PCB 输送到芯片的中心。基板中的电源/接地引脚分配和参考平面层堆叠旨在限度地减少寄生电阻和电感,从而限度地减少芯片上电源电压的变化。本节讨论由基板电感引起的交流波动。基板电阻还会导致直流电压下降,这将在后续部分中进行讨论。