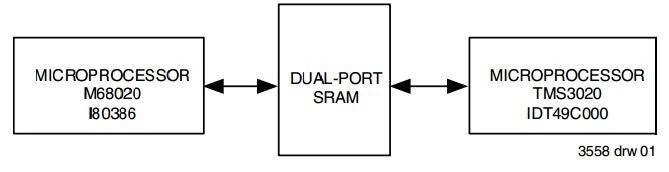

由于其高带宽和消息访问灵活性,双端口 SRAM 用于链接多个高性能

处理器和系统。

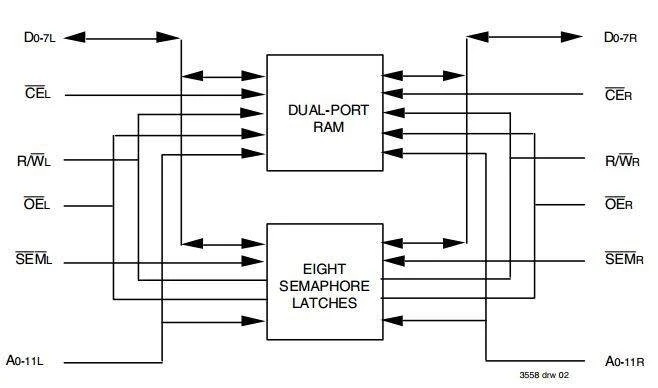

IDT 生产多种配置的双端口 SRAM,所有配置均由一个带有两组地址、数据和控制信号的 SRAM 组成。

由于其高带宽和消息访问灵活性,双端口 SRAM 用于链接多个高性能处理器和系统。Integrated Device Technology 生产多种配置的双端口 SRAM,所有配置均由一个带有两组地址、数据和控制信号的 SRAM 组成。这允许两个处理器在各自的地址空间中共享同一物理

内存块。两个处理器可以同时异步地访问两个内存位置中的数据。这种方法明显优于分立部件的设计,在分立部件的设计中,两个处理器必须通过仲裁来同步才能访问

总线,该总线用于访问标准单端口 RAM 中的一个位置。

仲裁

考虑一个多处理器系统,其中每个处理器都可以访问相同的数据。当多个处理器同时需要同一数据时,仲裁方案对于解决这种情况是必要的。解决仲裁问题的不同方法有不同的权衡,并且适合不同的应用。这些解决方案包括无仲裁、硬件解决方案、软件解决方案及其组合。

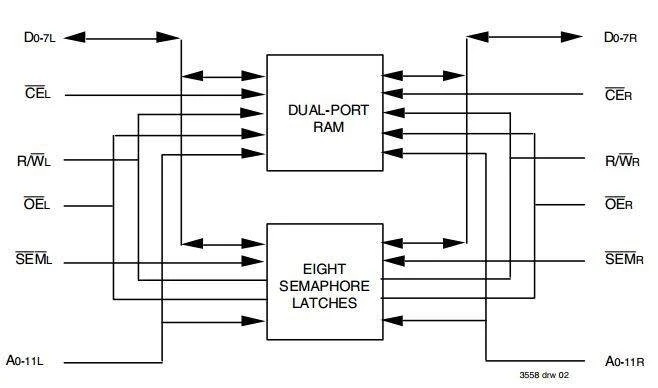

IDT71342 的功能描述

IDT71342 是一款具有信号量逻辑的快速双端口 4K x 8 CMOS 静态 SRAM,采用 52 引脚 PLCC 和 64 引脚 TQFP 封装。信号量逻辑可用于将双端口 SRAM 的部分分配到一侧或另一侧,并用于代替其他双端口设计中使用的地址仲裁逻辑。信号量由软件控制。因此,这种方法有几个缺点,包括分配任意大小的多个块以及没有处理器等待状态或繁忙逻辑。

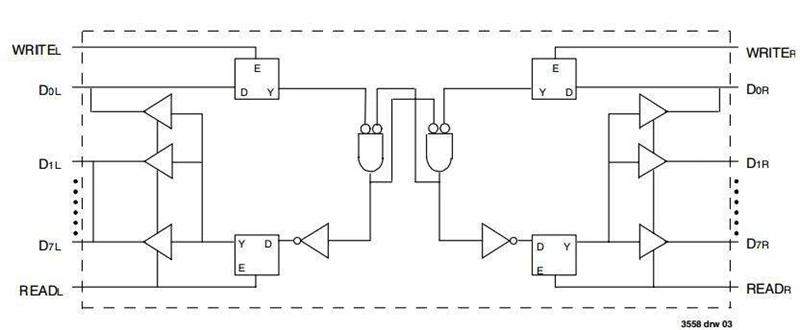

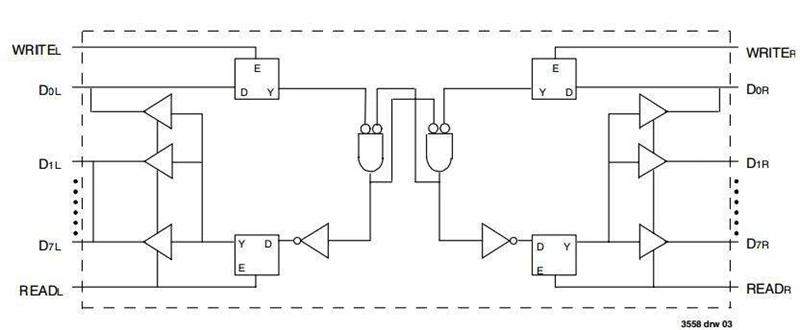

信号量标志如何工作

信号量逻辑由一组八个锁存器提供。这些锁存器可用于将标志或令牌从一个端口传递到另一个端口,以指示 SRAM 块正在使用中。内部电路防止标志同时在两个方向上传递。信号量为称为“令牌传递分配”的使用分配方法提供硬件辅助。在此方法中,信号锁存器的状态用作指示 SRAM 块正在使用的令牌。如果 Lport 上的处理器想要使用 SRAM 块,它会尝试设置请求令牌的锁存器。然后处理器检查锁存器以查看是否成功设置信号量。如果是,则处理器继续读取和/或写入该块。如果处理器未能成功设置锁存器,这意味着 R 端口首先设置了它,拥有令牌并且正在使用该块。L端口继续测试,直到成功,表明R端口已经释放了令牌,不再使用该块。

信号量的使用

信号量为硬件和软件级别的各种问题提供了有用的解决方案。以下选择重点介绍了信号量的一些优点,从提高性能到提供其他设计所不具备的功能。

有多种方法可以处理双端口 SRAM 仲裁。有效技术的选择涉及需要什么粒度的地址仲裁、是否使用处理器以及

存储器访问周期时序施加什么约束。信号量提供了一种替代方案,可以实现更高性能的系统并提供其他方式无法实现的功能。