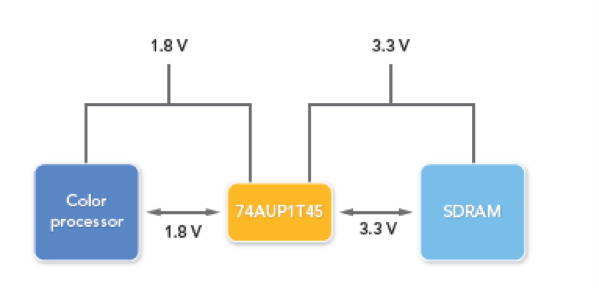

将电压从低电平转换为高电平或从高电平转换为低电平的逻辑器件也传输数据。数据传输可以在一个方向(单向)或两个方向(双向)进行。电压转换器配备有两个电源电压,每个电源电压支持不同的电压范围,可用于从低到高或从高到低的转换,并且通常提供支持单向或双向电平转换的版本。一些双向转换器具有控制数据方向的方向引脚 (DIR)。设置 DIR 引脚可设置转换方向:从 A 端口到 B 端口或从 B 端口到 A 端口。图 1 显示了一台数码相机,它使用 NXP 74AUP1T45 在使用 1.8 V 信号的色彩处理器和使用 3.0 V 信号的内存子系统之间转换信号。3V 信号。74AUP1T45 是一款单位收发器,具有两个数据 I/O(A 和 B)、一个 DIR 控制输入以及双电源引脚 VCC(A) 和 VCC(B)。VCC(A) 和 VCC(B) 均可提供 1.1V 至 3.6V 之间的任何电压,使该器件适合在任何低压节点(1.2、1.5、1.8、2.5 或 3.3V)之间连接。DIR 上的高信号允许从 A 到 B 的传输,DIR 上的低信号允许从 B 到 A 的传输。

图 1 在数码相机中使用 DIR 引脚进行双向电平转换

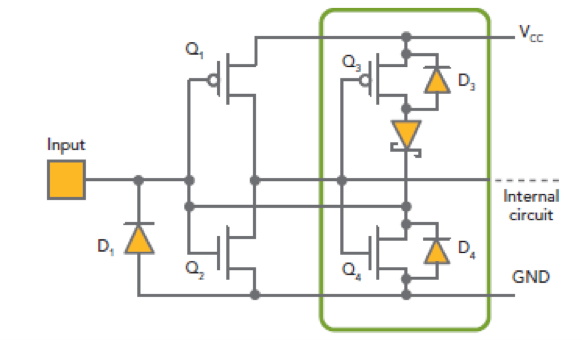

许多标准逻辑供应商都提供配备 DIR 引脚的双向转换器。例如,NXP AUP、AVC、LVC 和 ALVC 系列支持 0.8 至 5.5 V 的混合电压设计。一个器件的输出信号可以根据需要从高电平转换为低电平或从低电平转换为高电平,以匹配输入阈值。选项包括 1、2、4、8 或 16 位格式,覆盖 0.8 至 3.6 V 和 1.2 至 5.5 V 的转换范围。这些结果完全覆盖使用 1.2、1.8、2.5、 3.3 和 5.0 V。具有 DIR 引脚的器件中需要注意的另一件事是集成 IOFF 电路,该电路可以消除在挂起或掉电模式期间禁用输出时产生的破坏性回流电流。在大多数情况下,配备 DIR 引脚的器件是有源器件,一些双向转换器,尤其是较新的 CMOS 系列中的双向转换器,还配备了总线保持电路(图 2),可确保输入浮动时定义的逻辑电平。这可以防止输入电压在阈值电压附近浮动,从而损坏器件。

图 2 较新 CMOS 系列的总线保持电路

型号中带有“H”的恩智浦产品具有总线保持电路。NXP LVC 和 AVC 系列中的有源总线保持电路通过将未使用的数据输入保持在有效逻辑电平来防止浮动输入。总线保持电路充当输入锁存器,如果输入为三态或保持高阻抗,则保留驱动的数据。初加电时,无法保证总线保持锁存器的逻辑状态;它可能上电高或低。如果需要默认逻辑状态,则还需要外部电阻,并且这些电阻的大小应足以超速输入的总线保持电流,以避免争用问题。免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。