在现代电子系统设计中,ADC(模拟 - 数字转换器)和 FPGA(现场可编程门阵列)之间的 LVDS(低压差分信号)接口设计至关重要。合理的 LVDS 接口设计能够确保数据的高速、可靠传输,从而提升整个系统的性能。本文将详细阐述 ADC 和 FPGA 之间 LVDS 接口设计需要考虑的因素,包括 LVDS 数据标准、LVDS 接口数据时序违例解决方法以及硬件设计要点。

LVDS(低压差分信号)标准是业界广泛采用的差分数据传输标准,它采用双线、低摆幅差分信号进行数据传输。LVDS 具有诸多优点,如低电源电压运行,这使得其功耗较低,符合现代电子设备对低功耗的要求;能够实现高速数据传输,可满足高速数据采集和处理系统的需求;具备良好的共模噪声抑制能力,可有效减少外界干扰对数据传输的影响;并且产生的噪音更少,有助于提高系统的电磁兼容性。

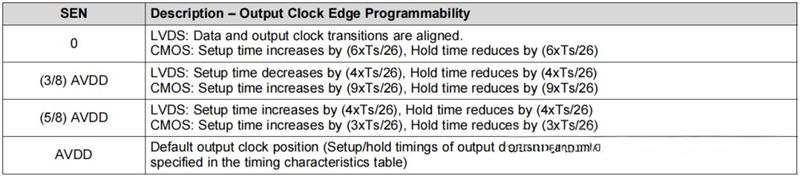

LVDS 是在 100Ω 的受控阻抗介质上进行基带数据传输,传输介质可以是 PCB 走线、背板或电缆。如图 1 所示,LVDS 输出由约 3.5mA 的电流源组成,该电流源驱动差分对。LVDS 接收器具有高直流输入阻抗,因此,LVDS 驱动器的大部分电流流过 100Ω 的终端电阻器,在接收器输入端产生约 350mV 的电压。

图 1:LVDS 发送器和接收器

ANSI/TIA/EIA - 644 - A(LVDS)标准对 LVDS 信号进行了定义。该标准主要规定了驱动器输出和接收器输入特性,是一个纯电气标准。它并不包含基本规范、协议甚至完整的电缆特性,因为这些都取决于具体的应用场景。这种灵活性使得 LVDS 标准能够在许多应用中轻松被采用,同时也允许参考标准根据所需的信号质量和媒体长度或类型指定所需的数据速率。

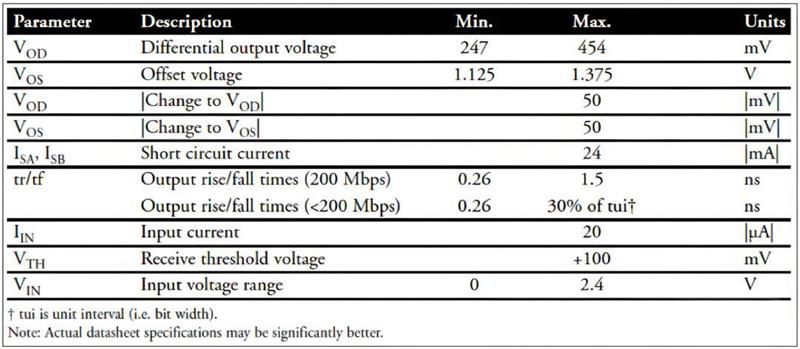

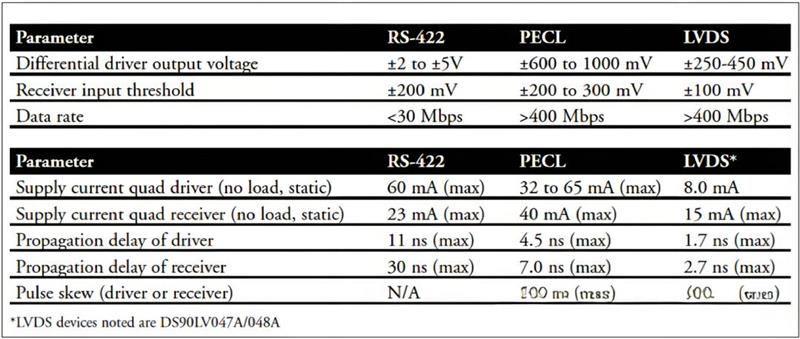

表 1:ANSI/TIA/EIA - 644(LVDS)标准

与 CMOS 等单端方案相比,LVDS 中使用的差分数据传输方法更不容易受到共模噪声的影响。差分传输使用两条具有相反电流和电压摆动的线来传输数据,而单端方案如 CMOS 仅使用一条线。LVDS 接收器只会查看两个信号之间的差异,从而可以有效消除共模噪声。另外,由于磁场的抵消,差分信号也倾向于比单端信号辐射更少的噪声。此外,电流模式驱动器不易产生振铃和开关尖峰,进一步降低了噪声。

ANSI/TIA/EIA 标准基于一组限制性假设建议数据速率为 655Mbps,并基于无损耗介质提供了 1.923Gbps 的理论值。但实际数据传输的终速率和距离取决于介质的衰减特性和来自环境的噪声耦合。

表 2:LVDS 与其他信号标准的比较

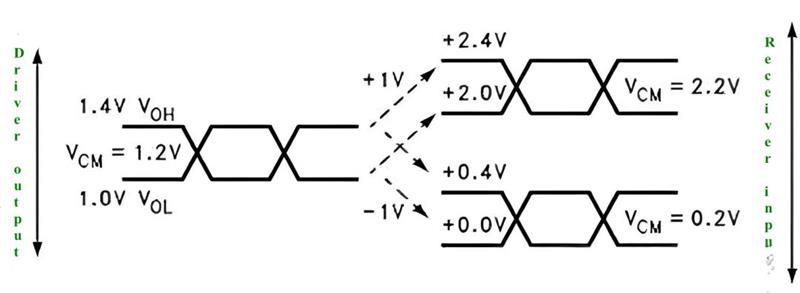

图 2:共模电压范围

当 LVDS 接收器中没有足够的建立和保持时间来捕获数据时,就会发生边沿捕获现象。这种现象可能是由于 LVDS 对之间的 PCB 走线长度不匹配导致的。例如,如果 6 个 DDR LVDS 对没有以相同的距离路由到 FPGA,则边沿捕获可能会发生在 12 位 ADC 中。在边沿捕获期间,一些数据位可能会改变其值,导致 FPGA 不能正确采样 ADC 数据。

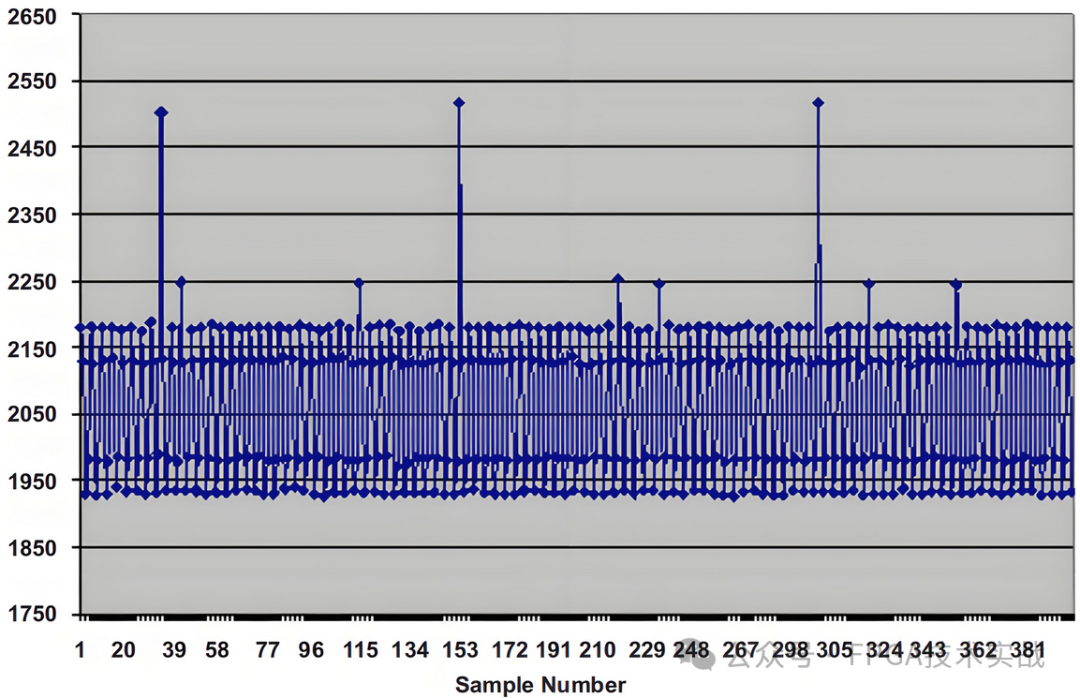

图 3:显示了从 ADS6129 12 位 ADC 在 FPGA 内捕获的边沿捕获数据

从图 3 中可以观察到,由于 ADC 数据的边缘捕获出现了峰值。在这种情况下,对比特 D6 和 D8 观察到边沿捕获。峰值是由于 D6 和 D8 位的建立和保持时间违规造成的。图中 x 轴表示采样数,y 轴表示 12 位 ADC 的信号幅度。

边沿捕获问题可以通过两种方法来解决。

通过使用 ADC 的串行接口或并行模式调整输出时钟边沿,ADC LVDS 数据可以相对于时钟延迟。只有调整输出时钟边沿才有可能改变所有 LVDS 对相对于输出时钟的建立和保持关系。图 4 提供了 ADS6129 串行模式下时钟位置偏移功能的详细信息。

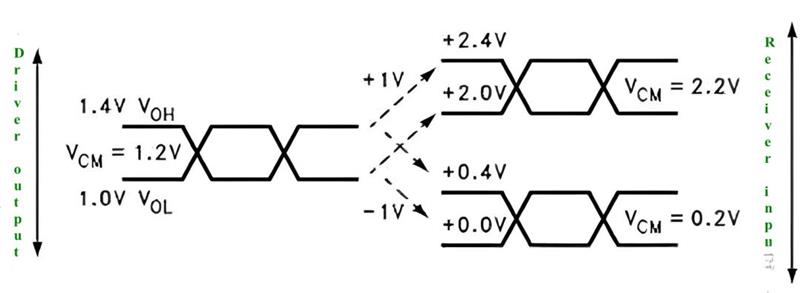

另外,ADS6129 为并行模式控制时,可以通过控制 SEN 引脚电压来控制时钟延迟,如表 3 所示。

表 3:SEN – 模拟控制引脚

解决边沿捕获问题的另一种方法是利用 FPGA 内部的延迟特性。FPGA 的每个 LVDS 对都有延迟组件。例如,Xilinx FPGA 具有称为 “IDELAY” 的延迟元件,可用于更改每个 LVDS 对的单独延迟。FPGA 的 IDELAY 非常灵活,可以插入任何 LVDS ADC 对和 FPGA 之间。对于图 2 所示的边沿捕获问题,LVDS 对 D6_D7 和 D8_D9 需要使用 IDELAY 组件进行延迟。此外,LVDS 数据对之间的偏斜也可以通过在 FPGA 内使用此 IDELAY 组件来补偿。

图 5:FPGA 延迟块与 ADC LVDS 数据

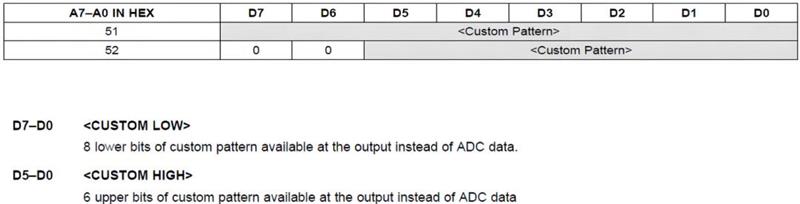

为了验证建立和保持时间,系统设计人员可以使用测试模式生成可以在 FPGA 内部验证的特定模式。在测试模式下,可以使用用户自定义模式对每个上升沿和下降沿的位翻转进行编程。这是用 FPGA 测试 ADC LVDS 数据接口健康状况的方法。图 6 提供了 ADS6129 和 ADS6149 的这种测试模式特征的信息。

图 6:ADC 内部的自定义测试模式选项

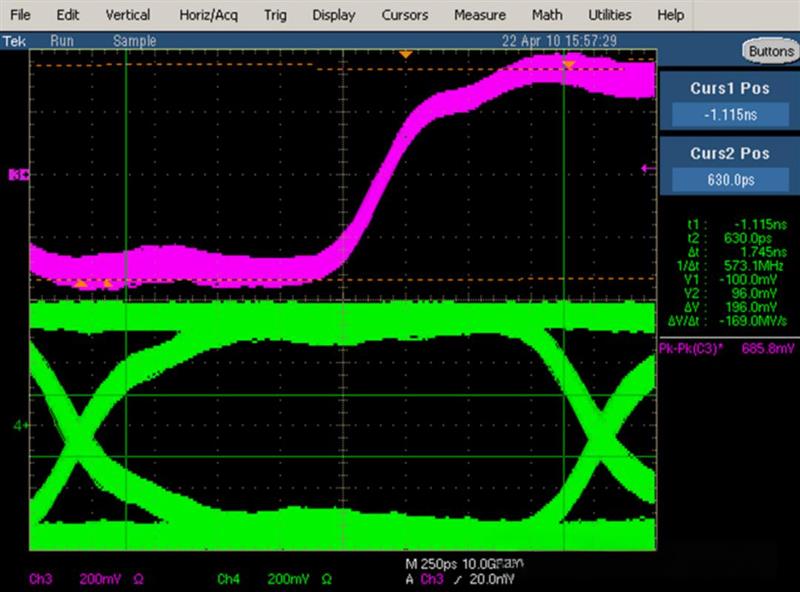

该测试可以确定 ADC 和 FPGA 之间的正确接口。如果测试模式通过,则可以认为 ADC LVDS 与 FPGA 的数据接口是正确的。图 7 显示了 10 MHz NORMAL 模拟输入信号的数字化数据眼图。

图 6:10MHz 正常输入模拟信号的数字化数据眼图

- 差分阻抗匹配:如果 ADC 输出和 FPGA 输入引脚之间的布线距离较大,则必须注意将差分阻抗保持在 100Ω 附近。差分对的总长度并不重要,但在指定内差分对之间的匹配很重要。此匹配规范取决于 ADC 采样率以及设置和保持时间裕度。

- 跨分割处的阻抗要求:在 ADC LVDS 输出和 FPGA 输入之间的任何跨分割处,差分特性阻抗应在 90Ω 至 110Ω 之间。由于 LVDS 信号的边缘速率很快,阻抗匹配非常重要,否则可能会导致信号反射和失真。

- PCB 层数选择:在 PCB 中使用至少 4 层。高速设计需要接地、电源和单端信号(如 CMOS)以及 LVDS 信号的单独层,这样可以减少信号之间的干扰,提高信号的完整性。

图 7:典型 4 层 PCB 层叠

- 通孔和转弯要求:LVDS 线路应尽量减少 PCB 通孔数量,使用 45 度转弯,避免 90 度转弯。过多的通孔和 90 度转弯可能会引入额外的电感和电容,影响信号的传输质量。

- 终端电阻选择:LVDS 信号在没有终端电阻器的情况下无法正常工作。的选择是使用 FPGA 的内部 100Ω 终端电阻器(如果可用)。对于内部 FPGA 终端电阻器,输入 LVDS 终端寄存器需要在 FPGA 粘合逻辑中设置为 “TRUE”。

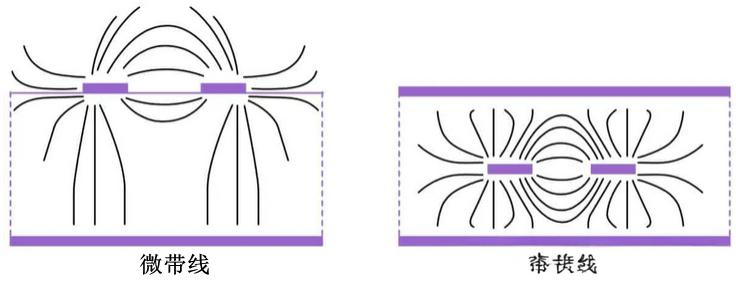

- 走线层选择:在顶层上布线高速走线可以避免通孔以及通孔引起的电感。然而,在中间层上布线高速走线有助于更好地抑制噪声。在带状线(中间层)而不是微带线(顶部 / 底部)上路由噪声信号有助于减少 EMI。

图 8:微带线与带状线

综上所述,在进行 ADC 和 FPGA 之间的 LVDS 接口设计时,需要综合考虑 LVDS 数据标准、时序违例解决方法以及硬件设计要点等多个方面的因素。只有这样,才能设计出高性能、可靠的 LVDS 接口,确保电子系统的稳定运行。